Como minimizar os parasitas em fontes de alimentação chaveadas

Contributed By DigiKey's North American Editors

2024-01-31

As fontes de alimentação chaveadas (modo de comutação) são populares por sua eficiência e flexibilidade. Elas também trazem desafios à medida que ampliam seu alcance para novas aplicações. Mais notavelmente, seu chaveamento de alta frequência pode induzir interferência eletromagnética (EMI) no restante do sistema. Além disso, os mesmos fatores que podem levar à EMI também reduzem a eficiência, prejudicando um dos principais benefícios das fontes de alimentação chaveadas.

Para evitar esses problemas, os projetistas devem tomar cuidado especial ao configurar a "malha quente", a parte do circuito da fonte de alimentação onde ocorre o chaveamento rápido. É essencial minimizar as perdas parasitas da malha quente devido à resistência em série equivalente (ESR) e à indutância em série equivalente (ESL). Isso pode ser feito escolhendo componentes de fonte de alimentação altamente integrados e um layout cuidadoso da placa de circuito impresso (PCI).

Este artigo apresenta as malhas quentes e as fontes de perda parasita, incluindo capacitores de acoplamento, transistores de efeito de campo (FETs) de potência e vias da PCI. Em seguida, ele mostra um exemplo de um conversor de energia altamente integrado da Analog Devices e apresenta vários layouts de PCI e seus efeitos sobre os parâmetros parasitas. Ele conclui com dicas práticas para a redução dos valores de ESR e ESL.

Fundamentos das malhas quentes das fontes de alimentação chaveadas

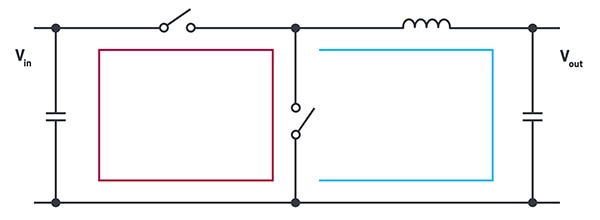

Qualquer projeto de fonte de alimentação que envolva correntes de chaveamento rápido, como conversores boost, buck-boost e flyback, terá malhas quentes com correntes de chaveamento em altas frequências. Esse conceito é ilustrado por meio de um conversor buck simplificado, também conhecido como conversor abaixador (Figura 1). A malha à esquerda (vermelho) contém todos os elementos de chaveamento; as correntes de alta frequência geradas pelo circuito estão contidas nele, formando a malha quente.

Figura 1: Um conversor buck simplificado ilustra o princípio de uma malha quente, destacado em vermelho. (Fonte da imagem: Analog Devices)

Figura 1: Um conversor buck simplificado ilustra o princípio de uma malha quente, destacado em vermelho. (Fonte da imagem: Analog Devices)

O aspecto "quente" vem das atividades significativas de conversão e chaveamento de energia que ocorrem nessa área do circuito, muitas vezes acompanhadas de geração de calor. O layout e o projeto adequados dessas malhas quentes são essenciais para minimizar a EMI e garantir uma operação eficiente da fonte de alimentação.

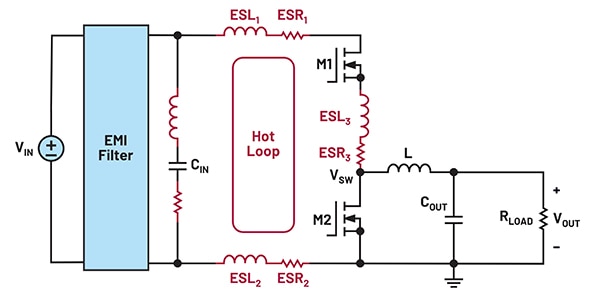

O circuito mais realista da Figura 2 mostra um conversor buck síncrono CC-CC. Para essa malha quente, os componentes físicos (marcados em preto) são o capacitor de entrada (CIN) e os FETs (MOSFETs) de chaveamento do tipo metal-óxido-semicondutor, M1 e M2.

Figura 2: As malhas quentes na prática incluem inevitavelmente parâmetros parasitas, mostrados em vermelho. (Fonte da imagem: Analog Devices)

Figura 2: As malhas quentes na prática incluem inevitavelmente parâmetros parasitas, mostrados em vermelho. (Fonte da imagem: Analog Devices)

Os parâmetros parasitas dentro da malha quente estão marcados em vermelho. A ESL está normalmente na faixa de nanohenry (nH), enquanto a ESR está na faixa de miliohm (mΩ). O chaveamento de alta frequência causa uma oscilação nas ESLs, resultando em EMI. A energia armazenada nas ESLs é então dissipada pelas ESRs, levando à perda de potência.

Minimização de parâmetros parasitas com componentes integrados

Essas impedâncias parasitas (ESRs, ESLs) ocorrem nos componentes e ao longo das trilhas da malha quente da PCI. Para minimizar esses parâmetros, os projetistas devem escolher cuidadosamente os componentes e otimizar o layout da PCI.

Uma maneira de atingir ambos os objetivos é usar componentes integrados. Isso elimina as trilhas da PCI necessárias para conectar componentes discretos e reduz a área total da malha quente. Ambos contribuem para reduzir a impedância parasita.

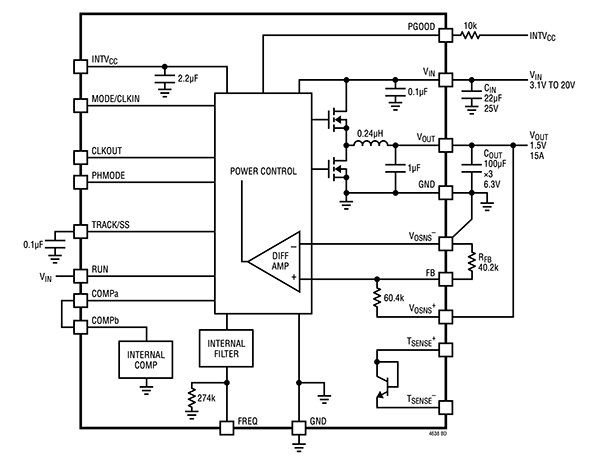

Um excelente exemplo de um componente altamente integrado é o regulador abaixador µModule LTM4638 da Analog Devices. Conforme ilustrado na Figura 3, esse regulador de chaveamento de 15 amperes (A) integra o controlador de chaveamento, os FETs de potência, o indutor e os componentes de suporte, tudo em um invólucro minúsculo que mede 6,25 × 6,25 × 5,02 milímetros (mm).

Figura 3: O regulador µModule LTM4638 integra muitos dos componentes necessários para um conversor buck. (Fonte da imagem: Analog Devices)

Figura 3: O regulador µModule LTM4638 integra muitos dos componentes necessários para um conversor buck. (Fonte da imagem: Analog Devices)

O LTM4638 incorpora vários outros recursos que reduzem as perdas parasitas. Esses incluem:

- Resposta rápida a transientes: Isso permite que o regulador ajuste rapidamente a tensão de saída em resposta a alterações na carga ou na entrada, minimizando a duração e o impacto das perdas parasitas por meio da transição rápida entre estados operacionais abaixo do ideal.

- Operação em modo descontínuo: Isso permite que a corrente do indutor caia para zero antes do início do próximo ciclo de chaveamento. Normalmente usado em condições de carga leve, esse modo reduz as perdas de chaveamento e do núcleo no indutor, desenergizando-o durante parte do ciclo.

- Rastreamento da tensão de saída: Permite que a saída do conversor siga uma tensão de entrada de referência. Ao controlar com precisão a subida e a descida da rampa na tensão de saída, esse recurso reduz a probabilidade de sobressinais ou sinais muito baixos que podem exacerbar as perdas parasitas.

Minimização de parâmetros parasitas com a colocação de componentes

A construção de um conversor buck síncrono com o LTM4638 requer a adição de capacitores de filtro na entrada e saída, CIN e COUT, respectivamente. O posicionamento desses capacitores pode ter um impacto significativo nos parâmetros parasitas.

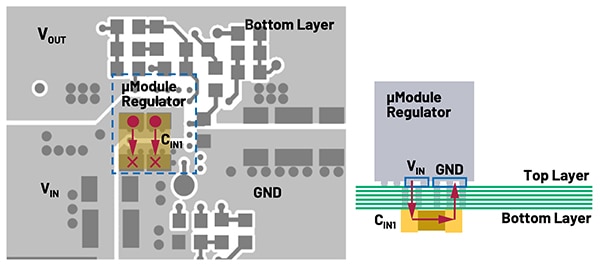

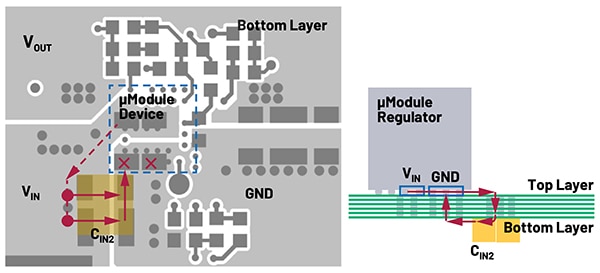

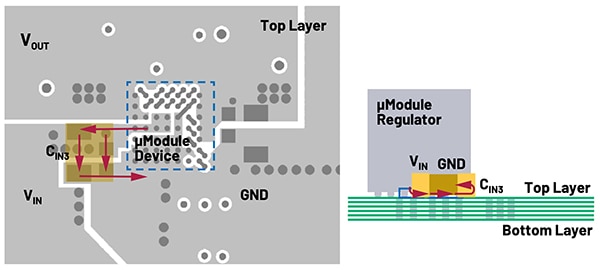

Os experimentos da Analog Devices com a placa de teste DC2665A-B para o LTM4638 ilustram o impacto do posicionamento do CIN.Desde então, o DC2665B-B substituiu essa placa, mas os mesmos princípios se aplicam. As Figuras 4 a 6 ilustram três layouts diferentes para o CIN e as malhas quentes correspondentes. As malhas quentes verticais 1 (Figura 4) e 2 (Figura 5) colocam o CIN na camada inferior, diretamente abaixo do regulador ou ao lado, respectivamente. A malha quente horizontal (Figura 6) coloca o capacitor na camada superior.

Figura 4: Vista inferior e lateral da malha quente vertical 1. O CIN está diretamente abaixo do regulador, conectado por meio de vias. (Fonte da imagem: Analog Devices)

Figura 4: Vista inferior e lateral da malha quente vertical 1. O CIN está diretamente abaixo do regulador, conectado por meio de vias. (Fonte da imagem: Analog Devices)

Figura 5: Vista inferior e lateral da malha quente vertical 2. O CIN está abaixo, mas ao lado do regulador, exigindo trilhas e vias na PCI. (Fonte da imagem: Analog Devices)

Figura 5: Vista inferior e lateral da malha quente vertical 2. O CIN está abaixo, mas ao lado do regulador, exigindo trilhas e vias na PCI. (Fonte da imagem: Analog Devices)

Figura 6: Vistas superior e lateral da malha quente horizontal. O CIN está na camada superior, conectando-se ao regulador por meio de trilhas. (Fonte da imagem: Analog Devices)

Figura 6: Vistas superior e lateral da malha quente horizontal. O CIN está na camada superior, conectando-se ao regulador por meio de trilhas. (Fonte da imagem: Analog Devices)

A malha quente vertical 1 tem o caminho mais curto e evita o uso de trilhas da PCI. Portanto, espera-se que ele tenha os parâmetros parasitas mais baixos. A análise de cada malha quente com o FastHenry a 600 kHz e 200 megahertz (MHz) revela que esse é o caso (Figura 7).

|

Figura 7: Como esperado, o caminho mais curto apresentou a menor impedância parasita. (Fonte da imagem: Analog Devices, modificada pelo autor)

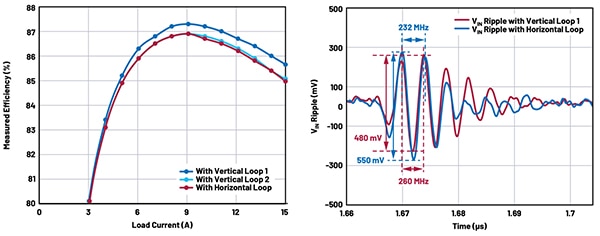

Embora esses parâmetros parasitas não possam ser medidos diretamente, seus efeitos podem ser previstos e testados. Especificamente, uma ESR menor deve levar a uma maior eficiência, enquanto uma ESL menor deve resultar em uma ondulação menor. A verificação experimental confirmou essas previsões, com a malha quente vertical 1 demonstrando melhor desempenho em ambas as métricas (Figura 8).

Figura 8: Os resultados experimentais confirmam que a malha quente vertical 1 alcança melhor eficiência e ondulação. (Fonte da imagem: Analog Devices)

Figura 8: Os resultados experimentais confirmam que a malha quente vertical 1 alcança melhor eficiência e ondulação. (Fonte da imagem: Analog Devices)

Minimização de parâmetros parasitas para componentes discretos

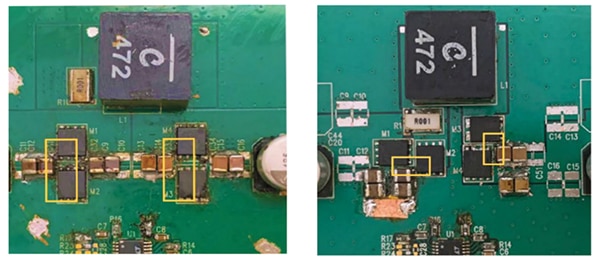

Embora os dispositivos integrados ofereçam muitas vantagens, algumas fontes de alimentação chaveadas exigem componentes discretos. Por exemplo, uma aplicação de alta potência pode exceder os limites dos dispositivos integrados. Nesses casos, o posicionamento e o tamanho do invólucro dos FETs de potência discretos podem afetar significativamente as ESRs e ESLs da malha quente. Esses impactos podem ser vistos ao testar duas placas de avaliação, ambas com controladores buck-boost síncronos de 4 comutadores de alta eficiência, conforme ilustrado na Figura 9:

- A placa de teste DC2825A é baseada no regulador buck-boost LT8390. Seus MOSFETs são colocados em paralelo, ou seja, na mesma orientação.

- A placa de teste DC2626A é baseada no regulador buck-boost LT8392. Ele tem dois pares de MOSFETs colocados em ângulos de 90˚.

Figura 9: O DC2825A (à esquerda) coloca seus MOSFETs em paralelo, enquanto o DC2626A (à direita) os coloca em ângulos de 90˚. (Fonte da imagem: Analog Devices)

Figura 9: O DC2825A (à esquerda) coloca seus MOSFETs em paralelo, enquanto o DC2626A (à direita) os coloca em ângulos de 90˚. (Fonte da imagem: Analog Devices)

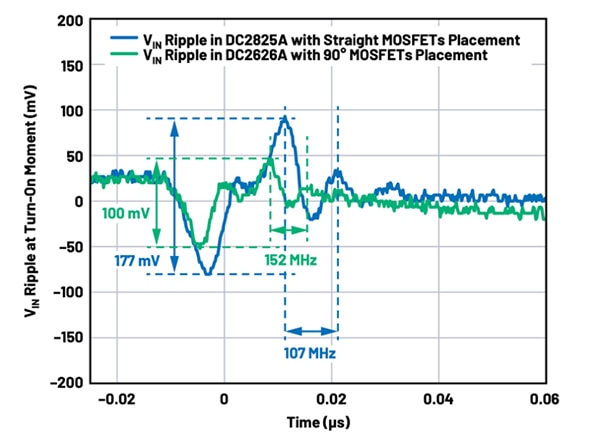

As duas placas foram testadas usando MOSFETs e capacitores idênticos em uma operação de redução de 36 a 12 volts a 10 A e 300 quilohertz (kHz). Os resultados mostraram que a colocação em 90˚ teve uma ondulação de tensão menor e uma frequência ressonante maior, indicando uma ESL menor da PCI devido a um caminho de malha quente mais curto (Figura 10).

Figura 10: O DC2626A, com seu layout MOSFET de 90˚, apresenta menor ondulação e maior frequência ressonante. (Fonte da imagem: Analog Devices)

Figura 10: O DC2626A, com seu layout MOSFET de 90˚, apresenta menor ondulação e maior frequência ressonante. (Fonte da imagem: Analog Devices)

Outras considerações sobre o layout

Colocações de vias na parte superior da malha quente também afetam a ESR e a ESL da malha. Em geral, adicionar mais vias reduz a impedância parasita da PCI. No entanto, a redução não é linearmente proporcional ao número de vias. Vias mais próximas dos pads terminais reduzem significativamente a ESR e a ESL. Portanto, várias vias devem ser colocadas perto dos pads dos componentes críticos (CIN e o µModule ou MOSFETs) para minimizar a impedância da malha quente.

Há muitas outras maneiras de afetar positivamente o desempenho elétrico e térmico. Para otimizar a malha quente, as práticas recomendadas incluem:

- Use grandes áreas de cobre na PCI para caminhos de alta corrente, incluindo VIN, VOUT e terra, para minimizar a perda de condução e o estresse térmico da PCI.

- Coloque uma camada dedicada de potencial terra embaixo da unidade.

- Use várias vias para interconexão entre a camada superior e outras camadas de energia para minimizar a perda de condução e reduzir o estresse térmico do módulo.

- Não coloque vias diretamente no pad, a menos que elas sejam tampadas ou revestidas.

- Use uma área de cobre separada como terra de sinal para os componentes conectados aos pinos de sinal, unindo o terra de sinal ao pino terra principal embaixo da unidade.

- Traga pontos de teste nos pinos de sinal para monitoramento.

- Mantenha a separação entre o sinal de clock e as trilhas de entrada de frequência para minimizar a possibilidade de ruído devido à diafonia.

Conclusão

Os parâmetros parasitas na malha quente influenciam muito o desempenho de uma fonte de alimentação chaveada. A minimização desses parâmetros é fundamental para obter alta eficiência e baixa EMI.

Uma das maneiras mais simples de atingir esses objetivos é usar módulos reguladores integrados. No entanto, as fontes de alimentação chaveadas normalmente exigem o uso de componentes filtrantes, como capacitores, por isso é essencial entender as implicações dos layouts de malha quente.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.