Como atender de forma simples e econômica os requisitos de temporização de circuitos de baixa potência usando SPXOs

Contributed By DigiKey's North American Editors

2021-08-25

A temporização de circuitos é uma função crítica exigida por uma ampla gama de dispositivos eletrônicos, incluindo microcontroladores, interfaces USB, Ethernet, Wi-Fi e Bluetooth, bem como dispositivos de computação e periféricos, dispositivos médicos, equipamentos de teste e medição, controle e automação industrial, a Internet das Coisas (IoT), vestíveis e eletrônicos de consumo. Projetar osciladores controlados por cristal para fornecer a temporização do sistema parece, a princípio, ser um exercício simples, mas os projetistas devem considerar uma série de parâmetros e requisitos de projeto ao combinar um cristal de quartzo com um CI oscilador.

As muitas considerações incluem impedância de movimento do cristal, modo ressonante, nível de acionamento e resistência negativa do oscilador. Para o layout do circuito, o projetista precisa considerar a capacitância parasitária da placa de circuito impresso, a inclusão de uma faixa de guarda ao redor do cristal e a capacitância integrada no chip. O projeto final precisa ser compacto e confiável, com um número mínimo de componentes, ter jitter com baixa raiz quadrada média (rms), e ser capaz de operar em uma ampla faixa de tensão de entrada com consumo mínimo de energia.

Uma solução é usar osciladores de cristal com invólucro simples (SPXOs). Otimizados para baixo consumo de energia e baixo jitter rms, além de funcionar em qualquer tensão entre 1,60 e 3,60 volts, estes osciladores de tensão contínua deixam os projetistas implementar soluções que requerem um esforço mínimo de projeto para se integrarem aos sistemas.

Este artigo discutirá brevemente alguns dos importantes requisitos de desempenho e desafios de projeto que devem ser satisfeitos para projetar circuitos de temporização com sucesso usando cristais de quartzo discretos e CIs de temporização. Em seguida, apresenta as soluções SPXO da Abracon e mostra como os projetistas podem utilizá-las para atender com eficácia e eficiência as necessidades de temporização dos sistemas eletrônicos.

Desafios de operação e projeto do oscilador de cristal

O consumo de energia é uma consideração importante em dispositivos sem fio pequenos, alimentados por bateria. Muitos desses dispositivos se baseiam em rádios e processadores com sistema de potência muito baixa (SoC) que podem suportar baterias com duração de vários anos. Além disso, minimizar o tamanho da bateria é importante para controlar o custo do dispositivo, já que a bateria pode ser o componente mais caro do sistema. Dito isto, a corrente do modo em espera é frequentemente a consideração mais importante da vida útil da bateria em sistemas pequenos sem fio, e o oscilador de clock frequentemente domina esta corrente. Portanto, a minimização do consumo de corrente do oscilador é fundamental.

Infelizmente, projetar osciladores de baixa potência pode ser um desafio. Uma maneira de economizar energia é minimizar a corrente de espera entrando em um estado de "desativação" e iniciando o oscilador conforme necessário. Entretanto, os osciladores de cristal não são simples de iniciar de forma rápida e confiável. Os projetistas precisam tomar cuidado para garantir que o oscilador extraia corrente baixa durante a espera e tenha características de partida confiáveis em todas as condições operacionais e ambientais.

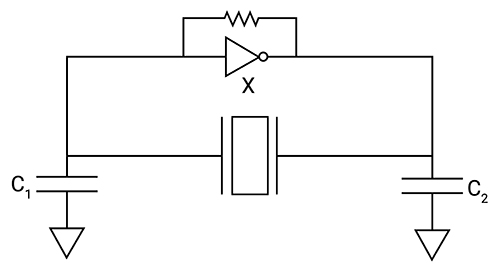

A configuração do oscilador Pierce é comumente usada em SoCs sem fio de baixa potência (Figura 1). Um oscilador Pierce é construído ao redor de um cristal (X) e capacitores de carga (C1 e C2), envolvidos com um amplificador inversor usando um resistor interno de realimentação. Sob as condições certas, quando a saída do amplificador é alimentada de volta à entrada, resulta em uma resistência negativa e ocorre oscilação.

Figura 1: Configuração básica do oscilador Pierce construído em torno de um cristal (X) e capacitores de carga C1 e C2. (Fonte da imagem: Abracon)

Figura 1: Configuração básica do oscilador Pierce construído em torno de um cristal (X) e capacitores de carga C1 e C2. (Fonte da imagem: Abracon)

Os cristais são estruturas complexas; esta discussão fornece apenas uma visão de alto nível e simplificada de seu funcionamento em osciladores.

A margem de ganho em malha fechada, Gm, pode ser usada como uma figura de mérito (FOM) para caracterizar a confiabilidade de um oscilador em relação a várias perdas. Também é chamada de "oscillation allowance" (OA). Um OA abaixo de 5 pode resultar em baixos rendimentos de produção e problemas de partida relacionados à temperatura. Os projetos com um OA de 20 ou mais são robustos, proporcionam um funcionamento confiável na faixa da temperatura de operação projetada e são insensíveis a variações de lotes de produção em termos de cristal e características de desempenho SoC.

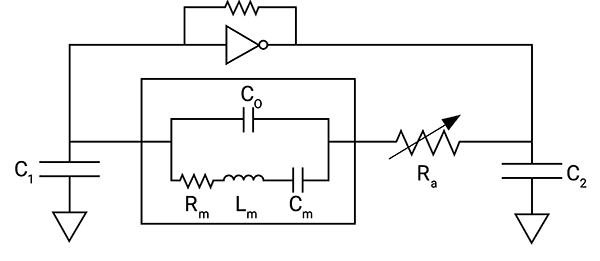

Para medir o OA de um oscilador, um resistor variável, Ra é adicionado ao circuito (Figura 2). O valor de Ra é aumentado até que o oscilador não possa iniciar. Esse é o valor utilizado para determinar o OA da seguinte forma:

![]() Equação 1

Equação 1

Onde:

Rn é a resistência negativa

Re é a resistência em série equivalente (ESR)

![]() Equação 2

Equação 2

![]() Equação 3

Equação 3

Onde a capacitância de carga,CL, é calculada utilizando:

![]() Equação 4

Equação 4

Onde Cs é a capacitância parasita do circuito, geralmente 3,0 a 5,0 picofarads (pF).

Figura 2: Oscilador Pierce mostrando o modelo de cristal expandido (no retângulo central) e o resistor ajustável (Ra) para medir o OA. (Fonte da imagem: Abracon)

Figura 2: Oscilador Pierce mostrando o modelo de cristal expandido (no retângulo central) e o resistor ajustável (Ra) para medir o OA. (Fonte da imagem: Abracon)

OA depende da ESR (Re), e a ESR depende do parâmetro Rm do cristal de quartzo e da capacitância de carga, CL. A influência do Rm e CL no OA aumenta para osciladores de baixa potência, tais como os utilizados em dispositivos sem fio. A medição de OA leva tempo e pode parecer prolongar o processo de desenvolvimento. Como resultado, ele pode ser ignorado, causando problemas de desempenho quando o sistema ou dispositivo entra em produção.

Além disso, o ajuste de um alto OA para garantir uma operação confiável do oscilador pode resultar em outros problemas. Por exemplo, um alto OA resultará em alto desempenho do circuito oscilador, mas as perdas de energia devido ao cristal podem ser negligenciadas. Essas perdas podem ser um fator significativo. Olhando para a Figura 2, a resistência de movimento do cristal, Rm, causa dissipação de potência à medida que a corrente circula através da resistência. A corrente e as perdas aumentam quando CL é maior. Os projetistas precisam alcançar um equilíbrio entre as perdas de energia no cristal e um valor razoável para OA.

Evitando o jitter

Ao projetar os osciladores de cristal de quartzo, é importante entender e minimizar o jitter. Há dois tipos de jitter, ambos tipicamente medidos como valores rms:

- Jitter ciclo a ciclo: também chamado de jitter de fase, é a máxima diferença de tempo entre vários períodos de oscilação medidos, geralmente medidos ao longo de um mínimo de 10 períodos.

- Jitter de período: esta é a mudança máxima de uma borda de clock e é medida em cada período, mas não em vários períodos.

As principais fontes de jitter nos osciladores de cristal de quartzo incluem ruído da fonte de alimentação, harmônicas inteiras da frequência do sinal, condições inadequadas de carga e terminação, ruído do amplificador e certas configurações de circuitos. Dependendo da fonte, há vários métodos que podem ser empregados para minimizar o jitter:

- Uso de capacitores de derivação, contas de chip ou filtros de resistor-capacitor (RC) para controlar o ruído da fonte de alimentação.

- Em aplicações críticas que exigem muito pouco jitter, é importante estabelecer um método para controlar os harmônicos (além do escopo deste artigo).

- Reduzir a potência refletida de volta à saída, otimizando as condições de carga e terminação.

- Evitar projetos que incluam malhas de captura de fase, multiplicadores ou recursos programáveis, pois tendem a aumentar o jitter.

Osciladores de cristal de tensão contínua

Os projetistas de sistemas com tensão de polarização variável entre 1,60 e 3,60 volts podem se beneficiar do uso dos SPXOs ASADV, ASDDV e ASEDV da Abracon (Figura 3). Estas famílias SPXO cobrem diferentes faixas de frequência; 1,25 megahertz (MHz) a 100 MHz para os dispositivos ASADV, e 1 MHz a 160 MHz para os dispositivos ASDDV e ASEDV. Eles são compatíveis com RoHS/RoHS II e vêm em invólucros de montagem em superfície cerâmica (SMD) hermeticamente seladas. Sua estabilidade de frequência é de ±25 partes por milhão (ppm) em toda sua faixa de temperatura operacional de -40 °C a +85 °C.

Figura 3: Os SPXOs ASADV (mostrado), ASDDV e ASEDV são encapsulados em invólucros cerâmicos hermeticamente selados e podem operar de -40 °C a +85 °C. (Fonte da imagem: Abracon)

Figura 3: Os SPXOs ASADV (mostrado), ASDDV e ASEDV são encapsulados em invólucros cerâmicos hermeticamente selados e podem operar de -40 °C a +85 °C. (Fonte da imagem: Abracon)

O ASADV mede 2,0 x 1,6 x 0,8 milímetros (mm), o ASDDV mede 2,5 x 2,0 x 0,95 mm, e o ASEDV mede 3,2 x 2,5 x 1,2 mm. Estas três séries estão disponíveis com uma variedade de faixas comuns de temperatura de operação, opções de estabilidade e um formato de saída compatível com CMOS/HCMOS/LVCMOS.

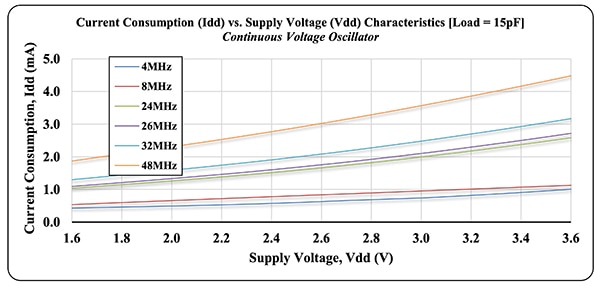

É importante notar que as famílias ASADV, ASDVD e ASEDV são otimizadas para operação com baixa corrente (Figura 4). A função ativar/desativar a saída reduz a corrente para apenas 10 microamperes (μA) quando desativada. Eles têm um tempo máximo de partida de 10 milissegundos (ms).

Figura 4: Mostra o consumo de corrente do ASEDV versus a tensão de alimentação que é típico do desempenho desta família de SPXOs (medido a 25 °C ±3 °C). (Fonte da imagem: Abracon)

Figura 4: Mostra o consumo de corrente do ASEDV versus a tensão de alimentação que é típico do desempenho desta família de SPXOs (medido a 25 °C ±3 °C). (Fonte da imagem: Abracon)

Todas as três famílias de SPXOs têm um consumo de corrente particularmente baixo. Para o ASADV, a corrente máxima (medida em uma carga de 15 pF a 25 °C) varia de 1,0 miliamperes (mA) a 1,25 MHz e uma tensão de alimentação de 1,8 volts, para 14,5 mA a 81 MHz e uma tensão de alimentação de 3,3 volts. Para o ASDDV e ASEDV, a corrente máxima varia de 1,0 mA a 1 MHz e uma tensão de alimentação de 1,8 volts, para 19 mA a 157 MHz e uma tensão de alimentação de 3,3 volts.

Os dispositivos podem acionar várias cargas e ter bom desempenho contra interferência eletromagnética (EMI) e baixo jitter. Eles são especificados para um jitter de fase rms <1,0 picossegundo (ps) e um jitter de período de 7,0 ps, máximo.

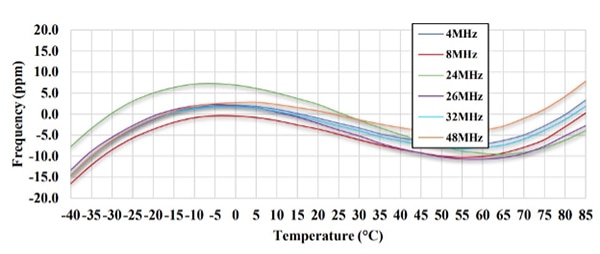

Os SPXOs também proporcionam boa estabilidade de frequência em toda sua faixa de temperatura operacional (Figura 5). Em muitas aplicações, estes osciladores podem ser usados como soluções prontas, necessitando de pouco trabalho de projeto. Eles também eliminam a necessidade de selecionar osciladores específicos de polarização e removem as variações de frequência dependentes da polarização.

Figura 5: Estes SPXOs têm boa estabilidade de frequência em toda a faixa de temperatura de operação. Este gráfico para a família ASEDV é típico. (Fonte da imagem: Abracon)

Figura 5: Estes SPXOs têm boa estabilidade de frequência em toda a faixa de temperatura de operação. Este gráfico para a família ASEDV é típico. (Fonte da imagem: Abracon)

Finalmente, quando o choque e a vibração não são considerações críticas, os osciladores de cristal ASADV, ASDVD e ASEDV de tensão contínua para montagem em superfície podem ser usados para fornecer alternativas de baixo custo aos osciladores de sistemas microeletromecânicos (MEMS).

Conclusão

Os projetistas necessitam de osciladores precisos e confiáveis para fornecer uma temporização estável em uma ampla gama de aplicações e temperaturas de operação. Os osciladores discretos controlados por cristal podem satisfazer as características de desempenho necessárias, mas o projeto eficaz com cristais pode ser tecnicamente difícil, demorado, desnecessariamente caro e subestimado no que diz respeito ao fator forma.

Como mostrado, os projetistas podem utilizar SPXOs integrados de baixa potência que formam soluções prontas de temporização com boa estabilidade de frequência em uma ampla faixa de temperatura operacional. Usando SPXOs, os projetistas podem reduzir a quantidade de componentes, diminuir o tamanho da solução, reduzir os custos de montagem e melhorar a confiabilidade.

Leitura recomendada

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.