Como usar os SoCs FPGA para Sistemas Seguros e Conectados em Tempo Real

Contributed By DigiKey's North American Editors

2023-02-16

Matrizes de portas programáveis no campo (FPGAs), subsistemas de unidades microcontroladoras RISC-V (MCU) com capacidade Linux, arquiteturas avançadas de memória e interfaces de comunicação de alto desempenho são ferramentas importantes para os projetistas. Isso é particularmente verdadeiro para projetistas de sistemas conectados seguros, sistemas críticos para a segurança e uma ampla gama de sistemas determinísticos estritos em tempo real como inteligência artificial (IA) e aprendizagem de máquinas (ML).

Entretanto, a integração desses diversos elementos em um sistema seguro, conectado e determinístico pode ser uma atividade desafiadora e demorada, assim como o estabelecimento das interconexões de alta velocidade para os diversos elementos do sistema. Os projetistas precisam incluir uma unidade de gerenciamento de memória, unidade de proteção de memória, capacidade de inicialização segura e transceptores de classe gigabit para conectividade de alta velocidade. O projeto precisará de gerenciamento e controle ativo e estático de energia e das correntes de partida. Alguns projetos exigirão operação na faixa de temperatura comercial ampliada de 0 °C a +100 °C de temperatura da junção (TJ), enquanto os sistemas em ambientes industriais precisarão operar com TJ de -40 °C a +100 °C.

Para enfrentar esses e outros desafios, os projetistas podem recorrer aos dispositivos SoC (Sistema sobre Chip) FPGA que combinam baixo consumo de energia, eficiência térmica e segurança de grau de defesa para sistemas inteligentes, conectados e determinísticos.

Este artigo revisa a arquitetura de um SoC FPGA e como ele suporta o projeto eficiente de sistemas conectados e determinísticos. Em seguida, apresenta brevemente o poder de processamento do EEMBC CoreMark-Pro versus o benchmark de consumo de energia, juntamente com uma visão do benchmark de desempenho de um SoC FPGA representativo. Ele analisa como a segurança é introduzida nesses SoCs FPGA e detalha exemplos de SoCs FPGA da Microchip Technology, juntamente com uma plataforma de desenvolvimento para acelerar o processo de projeto. Encerra com uma breve listagem de placas de expansão da MikroElektronika que podem ser usadas para implementar uma gama de interfaces de comunicação, bem como a capacidade de localização pelo Sistema Global de Navegação por Satélite (GNSS).

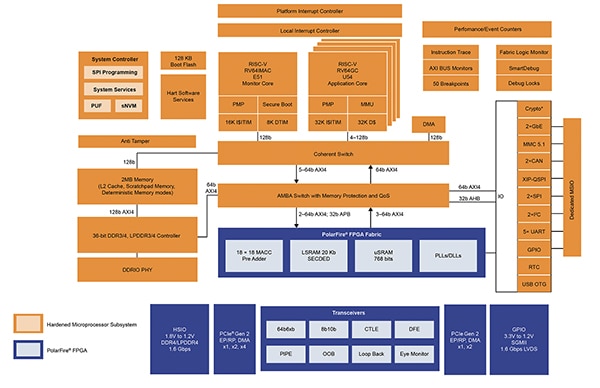

SoCs construídos com tecido FPGA

O “chip” para esse SoC é um tecido FPGA que contém os elementos do sistema, desde a FPGA até o subsistema RISC-V MCU que é construído com uma lógica FPGA reforçada. O subsistema MCU inclui um cluster RISC-V MCU quad-core, um núcleo de monitor RISC-V, um controlador de sistema e um subsistema de memória determinístico de nível 2 (L2). A FPGA nesses SoCs inclui até 460 K de elementos lógicos, transceptores com até 12,7 gigabits por segundo (Gbps) e outros blocos de entrada/saída (E/S), incluindo E/S de uso geral (GPIO) e PCIe 2 (Peripheral Component Interconnect Express). A arquitetura geral é projetada para a confiabilidade. Inclui correção de erro simples e detecção de erro duplo (SECDED) em todas as memórias, análise de potência diferencial (DPA), proteção de memória física e 128 quilobits (Kbits) de memória flash de inicialização (Figura 1).

Figura 1: Todos os elementos desse SoC da FPGA, incluindo os subsistemas RISC-V, são implementados no tecido da FPGA. (Fonte da imagem: Microchip Technology)

Figura 1: Todos os elementos desse SoC da FPGA, incluindo os subsistemas RISC-V, são implementados no tecido da FPGA. (Fonte da imagem: Microchip Technology)

A Microchip oferece seu ecossistema Mi-V (se diz "my five") de ferramentas de terceiros e recursos de projeto para apoiar a implementação dos sistemas RISC-V. Foi construído para acelerar a adoção da arquitetura do conjunto de instruções RISC-V (ISA) para núcleos RISC-V reforçados e para núcleos flexíveis RISC-V. Elementos do ecossistema Mi-V incluem acesso a:

- Licenças de propriedade intelectual (PI)

- Hardware

- Sistemas operacionais e middleware

- Depuradores, compiladores e serviços de projeto

Os MCUs RISC-V reforçados no SoC FPGA incluem várias capacidades de depuração como a interface avançada extensível configurável em tempo de execução passivo (AXI) e rastreamento de instrução. O AXI permite que os projetistas monitorem os dados que estão sendo escritos ou lidos de várias memórias e saibam quando estão sendo escritos ou lidos.

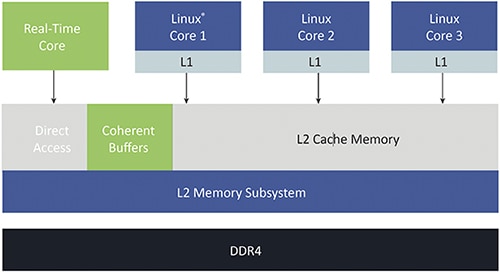

O subsistema RISC-V MCU utiliza uma pipeline de cinco estágios de instrução emissão em ordem. Não é vulnerável a explorações de Spectre ou Meltdown que possam afligir arquiteturas fora de ordem. Todas as cinco MCUs são coerentes com o subsistema de memória, suportando uma mistura de sistemas em tempo real em modo de multi-processamento assimétrico determinístico (AMP) e Linux. As capacidades do subsistema RISC-V incluem (Figura 2):

- Executar Linux e operações estritas em tempo real

- Configurar L1 e L2 como memória determinista

- Subsistema de memória DDR4

- Desabilitar/habilitar previsões de ramal

- Operação de pipeline em ordem

Figura 2: O subsistema RISC-V inclui vários elementos de processamento e memória. (Fonte da imagem: Microchip Technology)

Figura 2: O subsistema RISC-V inclui vários elementos de processamento e memória. (Fonte da imagem: Microchip Technology)

Mais processamento com menos energia

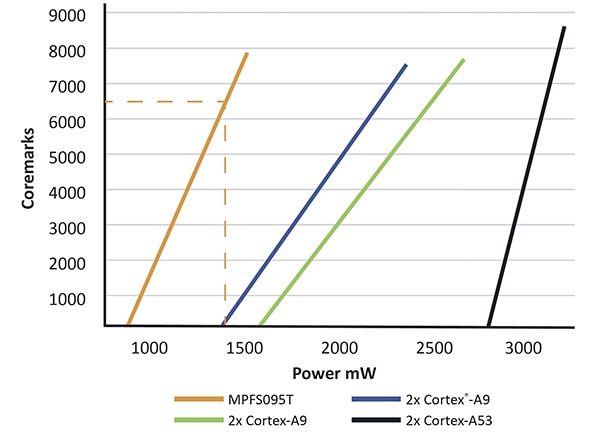

Além de seus benefícios de operação do sistema, incluindo suporte para processamento estrito e em tempo real, esses SoCs FPGA são altamente eficientes em termos energéticos. O benchmark do EEMBC CoreMark-PRO é um padrão da indústria para comparar a eficiência e o desempenho das MCUs em sistemas embarcados. Ele foi projetado especificamente para comparar o desempenho do hardware e para substituir a referência Dhrystone.

As cargas de trabalho do CoreMark-PRO incluem uma diversidade de características de desempenho, paralelismo no nível de instrução e utilização de memória baseada em quatro cargas de trabalho de ponto flutuante e cinco cargas de trabalho inteiras comuns. As cargas de trabalho em ponto flutuante incluem uma rotina de álgebra linear derivada do LINPACK, uma transformação de Fourier rápida, um algoritmo de rede neural para avaliação de padrões e uma versão melhorada do benchmark de malhas Livermore. Compressão JPEG, um analisador XML, compressão ZIP e um algoritmo de hash seguro de 256 bits (SHA-256) formam a base das cargas de trabalho inteiras.

Os modelos MPFSO95T desses SoC FPGAs, como o MPFS095TL-FCSG536E, podem fornecer até 6.500 Coremarks a 1,3 watt (Figura 3).

Figura 3: O SoC FPGA MPFS095T (linha laranja) fornece 6.500 Coremarks a 1,3 watts. (Fonte da imagem: Microchip Technology)

Figura 3: O SoC FPGA MPFS095T (linha laranja) fornece 6.500 Coremarks a 1,3 watts. (Fonte da imagem: Microchip Technology)

Considerações de segurança

As aplicações críticas de segurança e estritas em tempo real para esses SoCs FPGA requerem forte segurança, além de alta eficiência energética e poderosa capacidade de processamento. As funções básicas de segurança desses SoCs FPGA incluem análise diferencial de potência (DPA), programação de fluxo de bits resistente, um verdadeiro gerador de números aleatórios (TRNG) e uma função fisicamente não-clonável (PUF). Eles também incluem inicialização segura padrão e definida pelo usuário, proteção de memória física que fornece restrições de acesso à memória relacionadas ao estado de privilégio da máquina, incluindo modos de máquina, supervisor ou usuário, e imunidade contra ataques de Meltdown e Spectre.

A segurança começa com o gerenciamento seguro da cadeia de fornecimento, incluindo o uso de módulos de segurança de hardware (HSMs) durante os testes de pastilha e invólucro. O uso de um certificado de 768 bytes assinado digitalmente x.509 FPGA incorporado em cada SoC FPGA acrescenta à garantia da cadeia de fornecimento.

Inúmeros detectores de violação em chip estão incluídos nesses SoCs FPGA para garantir uma operação segura e confiável. Se uma violação for detectada, é emitida uma bandeira de violação que permite que o sistema responda conforme necessário. Alguns dos detectores de violação disponíveis incluem:

- Monitores de tensão

- Sensores de Temperatura

- Detectores de falha de clock e de freqüência de clock

- Detector ativo JTAG

- Detector ativo de malha

A segurança é ainda mais garantida com o padrão de criptografia avançada de 256 bits (AES-256) de contra-medidas de ataque de potência de correlação de blocos simétricos (CPA), capacidades de digestão criptográfica integrada para garantir a integridade dos dados, PUF integrado para armazenamento de chaves e capacidades de zeragem para o tecido FPGA e todas as memórias em chip.

Exemplos de SoC FPGA

A Microchip Technology combina essas capacidades e tecnologias em seus SoCs PolarFire com vários graus de velocidade, classificações de temperatura e vários tamanhos de invólucros para dar suporte às necessidades dos projetistas de uma ampla gama de soluções com elementos lógicos entre 25 K e 460 K. Estão disponíveis quatro graus de temperatura (todos classificados para TJ), faixa comercial ampliada de 0 °C a +100 °C, faixa industrial de -40 °C a +100 °C, faixa automotiva de -40 °C a +125 °C e faixa militar de -55 °C a +125 °C.

Os projetistas podem escolher entre dispositivos de grau de velocidade padrão, ou dispositivos de grau de velocidade -1, que são 15% mais rápidos. Estes SoCs FPGA podem ser operados a 1,0 volts para a operação de menor potência ou a 1,05 volts para maior desempenho. Estão disponíveis em uma gama de tamanhos de invólucros, incluindo 11 x 11 milímetros (mm), 16 x 16 mm, e 19 x 19 mm.

Para aplicações que necessitam de operação com temperatura comercial prolongada, operação com velocidade padrão e elementos lógicos de 254 K em um invólucro de 19 x 19 mm, os projetistas podem usar o MPFS250T-FCVG484EES. Para soluções mais simples que necessitam de elementos lógicos de 23 K, os projetistas podem recorrer ao MPFS025T-FCVG484E, também com operação de temperatura comercial prolongada e grau de velocidade padrão em um invólucro de 19 x 19 mm. O MPFS250T-1FCSG536T2 com elementos lógicos de 254 K é projetado para sistemas automotivos de alto desempenho e tem uma faixa de temperatura operacional de -40 °C a 125 °C e um grau de velocidade -1 para um clock 15% mais rápido, em um invólucro compacto de 16 x 16 mm com 536 bolas em um passo de 0,5 mm (Figura 4).

Figura 4: O MPFS250T-1FCSG536T2 de temperatura automotiva vem em uma invólucro de 16 x 16 mm com uma contagem de bola de 536 e um passo de 0,5 mm. (Fonte da imagem: Microchip Technology)

Figura 4: O MPFS250T-1FCSG536T2 de temperatura automotiva vem em uma invólucro de 16 x 16 mm com uma contagem de bola de 536 e um passo de 0,5 mm. (Fonte da imagem: Microchip Technology)

Plataforma de desenvolvimento SoC FPGA

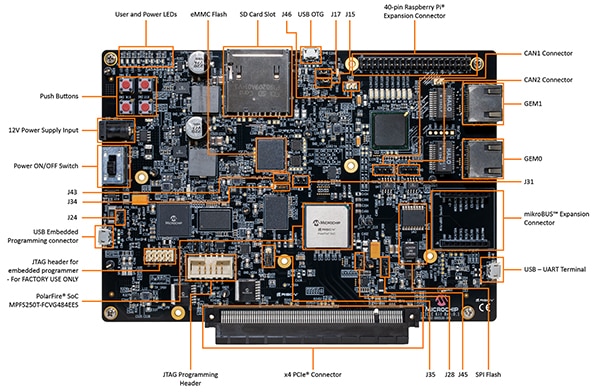

Para acelerar o projeto de sistemas com o SoC FPGA PolarFire, a Microchip oferece o kit Icicle SoC PolarFire MPFS-ICICLE-KIT-ES que permite a exploração do subsistema de microprocessador RISC-V de cinco núcleos com capacidade para Linux com execução em tempo real e baixa potência. O kit inclui uma licença Libero Silver gratuita que é necessária para avaliar projetos. Ele suporta recursos de programação e depuração em uma única linguagem.

Esses SoCs FPGA são suportados pelo kit de desenvolvimento de software do acelerador (SDK) VectorBlox que permite aplicações AI/ML de baixa potência e pequeno fator de forma. A ênfase está em simplificar o processo de projeto a ponto de os projetistas não precisarem ter experiência prévia em projetos de FPGA. O acelerador SDK da VectorBlox permite que os desenvolvedores programem redes neurais com eficiência energética usando C/C++. O kit Icicle tem inúmeros recursos para fornecer um ambiente de desenvolvimento abrangente, incluindo um sistema de sensor de energia várias trilhas para monitorar os vários domínios de energia, porta raiz PCIe e memórias na placa — incluindo LPDDR4, QSPI e eMMC Flash — para rodar Linux e Raspberry Pi e portas de expansão mikroBUS para uma série de opções de conectividade com e sem fio, além de extensões funcionais como a capacidade de localização GNSS (Figura 5).

Figura 5: Esse ambiente abrangente de desenvolvimento SoC FPGA inclui conectores para placas de expansão Raspberry Pi (parte superior direita) e mikroBUS (parte inferior direita). (Fonte da imagem: Microchip Technology)

Figura 5: Esse ambiente abrangente de desenvolvimento SoC FPGA inclui conectores para placas de expansão Raspberry Pi (parte superior direita) e mikroBUS (parte inferior direita). (Fonte da imagem: Microchip Technology)

Placas de expansão

Alguns exemplos de placas de expansão mikroBUS incluem:

MIKROE-986, para adicionar conectividade barramento CAN usando uma interface periférica serial (SPI).

MIKROE-1582, para a interface entre a MCU e um barramento RS-232.

MIKROE-989, para conexão com um barramento de comunicação RS422/485.

MIKROE-3144, suporta as tecnologias LTE Cat M1 e NB1 permitindo uma conectividade confiável e simples com dispositivos 3GPP IoT.

MIKROE-2670, permite a funcionalidade GNSS com recepção simultânea de constelações GPS e Galileo mais BeiDou ou GLONASS, resultando em alta precisão de posição em situações com sinais fracos ou interferência em desfiladeiros urbanos.

Conclusão

Os projetistas podem recorrer aos SoCs FPGA ao desenvolver sistemas conectados, críticos para a segurança e determinísticos em tempo real estritos. Os SoCs FPGA fornecem uma ampla gama de elementos do sistema, incluindo um tecido FPGA, subsistema MCU RISC-V com memórias de alto desempenho, interfaces de comunicação de alta velocidade e numerosas funções de segurança. Para ajudar os projetistas a começar, estão disponíveis placas de desenvolvimento e ambientes que incluem todos os elementos necessários, incluindo placas de expansão que podem ser usadas para implementar uma ampla gama de funções de comunicação e localização.

Leitura recomendada

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.