Maximize a densidade de potência e o desempenho em aplicações de conversores de comutação com MOSFETs duplos

2024-02-27

Os conversores de comutação industriais e automotivos e os acionadores de motor exigem transistores de efeito de campo de óxido-metal-silício (MOSFETs) que sejam pequenos, eficientes e gerem o mínimo de ruído elétrico. Uma abordagem de MOSFET duplo ajuda a atender a esses requisitos.

Ao colocar dois MOSFETs em um único invólucro, os MOSFETs duplos bem projetados consomem menos espaço na placa de circuito impresso (PCI), reduzem a indutância parasita e eliminam a necessidade de dissipadores de calor volumosos e caros, melhorando o desempenho térmico. Esses dispositivos podem comutar sem interferência a várias centenas de quilohertz (kHz), operar de forma estável em uma ampla faixa de temperatura e apresentar baixa corrente de fuga. No entanto, os projetistas devem entender suas características operacionais para aproveitar plenamente as vantagens dessas peças.

Este artigo apresenta exemplos de MOSFETs duplos da Nexperia e mostra como os projetistas podem usá-los para enfrentar os desafios de projetos robustos, de alta eficiência e com restrições de espaço. Ele discute maneiras de otimizar o projeto de circuitos e PCIs e fornece dicas sobre simulação eletrotérmica e análise de perdas.

Mais eficiência em alta velocidade de comutação

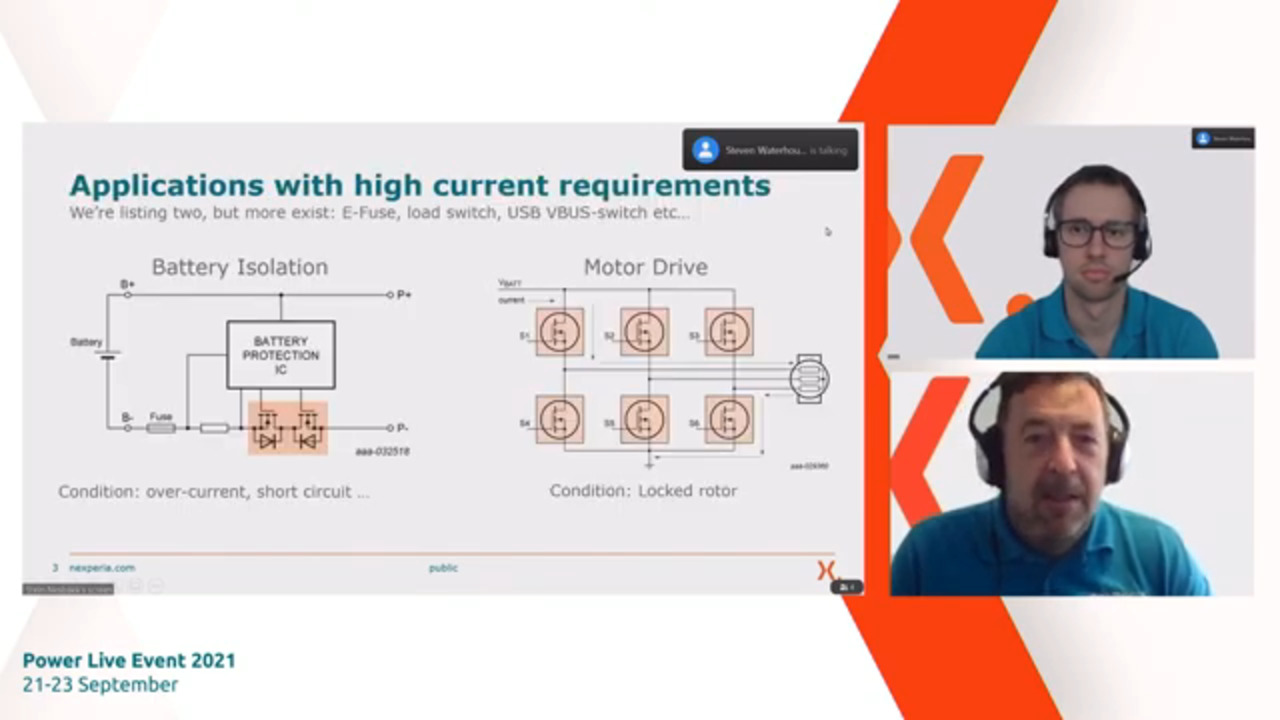

Os MOSFETs duplos são adequados para muitas aplicações automotivas (AEC-Q101) e industriais, incluindo conversores de comutação CC/CC, inversores de motor e controladores de válvulas solenoides. Essas aplicações podem usar MOSFETs duplos em pares de comutadores e topologias de meia ponte, entre outras configurações.

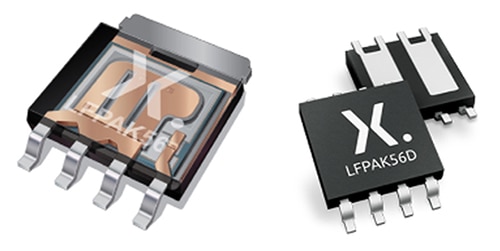

A série Nexperia LFPAK56D é um exemplo notável de dispositivos MOSFET duplos. Ela apresenta a tecnologia de clipe de cobre da Nexperia, que permite uma capacidade de corrente excepcional, baixa impedância do invólucro e alta confiabilidade (Figura 1, à direita). Esses clipes de cobre rígido melhoram a dissipação de calor do substrato do semicondutor por meio das juntas soldadas à placa de circuito impresso, permitindo que aproximadamente 30% do calor total removido flua pelos pinos de origem. As grandes seções transversais de cobre também diminuem a dissipação de potência ôhmica e amortecem a oscilação, reduzindo a indutância parasita da linha.

Figura 1: O invólucro LFPAK56D (à direita) integra dois MOSFETs independentes e usa estruturas de clipe de cobre semelhantes ao invólucro LFPAK56 de MOSFET único (à esquerda). (Fonte da imagem: Nexperia)

Figura 1: O invólucro LFPAK56D (à direita) integra dois MOSFETs independentes e usa estruturas de clipe de cobre semelhantes ao invólucro LFPAK56 de MOSFET único (à esquerda). (Fonte da imagem: Nexperia)

Como a maioria das peças destinadas a conversores de comutação de alta tensão, o LFPAK56D usa a tecnologia de superjunção. Esse projeto reduz a resistência "saturada" da fonte do dreno (RDS(on)) e os parâmetros da carga de porta-dreno (QGD), minimizando as perdas de potência. A operação de dois MOSFETs no mesmo substrato reduz ainda mais a resistência dreno-fonte.

Como MOSFETs de superjunção, a série LFPAK56D é robusta contra eventos de avalanche e tem uma ampla área de operação segura (SOA). Por exemplo, cada um dos MOSFETs de 100 volts no dispositivo TrenchMOS PSMN029-100HLX tem um RDS(on) de 29 miliohm (mΩ), pode suportar 68 watts e passar até 30 amperes (A).

A série LFPAK56D também usa a tecnologia SchottkyPlus da NXP para reduzir o comportamento de pico e a corrente de fuga. Por exemplo, o RDS(on) típico do PSMN014-40HLDX é de 11,4 mΩ, e a corrente de fuga dreno-fonte é de 10 nanoamperes (nA), extremamente baixa.

Para utilizar totalmente as altas correntes dos MOSFETs, a PCI deve ser projetada para dissipar o calor elevado e garantir conexões elétricas estáveis. As PCIs multicamadas com vias suficientes e trilhas grandes e espessas dos condutores de cobre garantem um alto desempenho térmico.

Evite a avalanche térmica

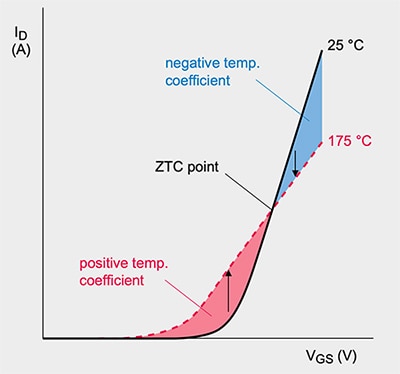

Embora os MOSFETs de potência totalmente ligados sejam termicamente estáveis, a avalanche térmica é um risco quando a corrente de dreno (ID) é baixa. Nesse estado operacional, o aquecimento localizado tende a diminuir a tensão limiar da porta-fonte (VGS(th)), o que significa que o dispositivo é ligado mais rapidamente. Isso cria uma situação de realimentação positiva em que a corrente adicional causa mais aquecimento e um VGS(th) ainda mais baixo.

A Figura 2 mostra esse efeito para uma tensão constante de dreno-fonte (VDS). À medida que o VGS aumenta, há um ID crítico conhecido como ZTC (coeficiente de temperatura zero). Acima dessa corrente, há realimentação negativa e estabilidade térmica (zona azul); abaixo dela, a queda de tensão limiar domina, resultando em pontos de operação termicamente instáveis que podem levar à avalanche térmica (zona vermelha).

Figura 2: Abaixo do ponto ZTC, o MOSFET pode entrar em avalanche térmica devido a uma queda do valor de VGS, induzida termicamente (área vermelha). (Fonte da imagem: Nexperia)

Figura 2: Abaixo do ponto ZTC, o MOSFET pode entrar em avalanche térmica devido a uma queda do valor de VGS, induzida termicamente (área vermelha). (Fonte da imagem: Nexperia)

Esse efeito reduz o valor de SOA em baixas correntes e altas tensões dreno-fonte. Essa não é uma preocupação significativa para operações de chaveamento rápido com uma inclinação acentuada de dV/dt. Entretanto, à medida que a duração da comutação aumenta, por exemplo, para reduzir a interferência eletromagnética, a instabilidade térmica se torna mais provável e potencialmente perigosa.

Menores perdas de comutação em altas frequências

Ao selecionar um MOSFET de superjunção para aplicações de chaveamento rápido, um valor baixo de QGD é essencial, pois isso reduz significativamente as perdas de comutação.

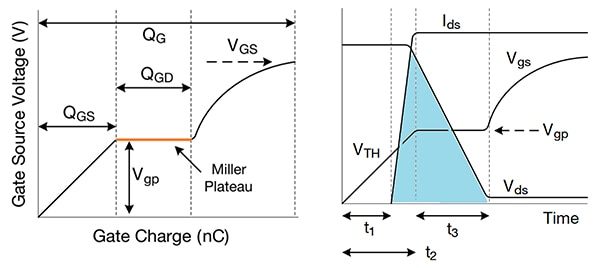

A alta perda de potência ocorre durante a comutação, quando mudanças significativas de tensão e corrente aparecem simultaneamente entre o dreno, a porta e a fonte. Um valor baixo de QGD resulta em um platô de Miller curto (Figura 3, à esquerda), levando a uma inclinação acentuada da comutação (dVds/dt) e, por fim, resultando em menor perda de energia dinâmica durante a ativação (Figura 3, área azul à direita).

Figura 3: Um platô de Miller curto (à esquerda) significa uma inclinação acentuada da comutação, resultando em baixas perdas dinâmicas (área azul à direita). Vgp é a tensão porta-fonte do platô de Miller; VTH é a tensão de limiar da porta; IDS é a corrente dreno-fonte. (Fonte da imagem: Vishay)

Figura 3: Um platô de Miller curto (à esquerda) significa uma inclinação acentuada da comutação, resultando em baixas perdas dinâmicas (área azul à direita). Vgp é a tensão porta-fonte do platô de Miller; VTH é a tensão de limiar da porta; IDS é a corrente dreno-fonte. (Fonte da imagem: Vishay)

Limitando a energia de avalanche e protegendo o MOSFET

No momento do desligamento de uma bobina de estator em uma aplicação de acionamento de motor, o campo magnético em colapso mantém o fluxo de corrente, gerando uma alta tensão de indução no MOSFET que se sobrepõe à tensão de alimentação (VDD). No entanto, a tensão de ruptura reversa (VBR) do diodo incorporado ao MOSFET limita essa alta tensão. No que é conhecido como efeito de avalanche, o MOSFET converte a energia magnética de saída em energia de avalanche (EDS) até que a corrente da bobina caia para zero. Isso pode superaquecer rapidamente o cristal semicondutor.

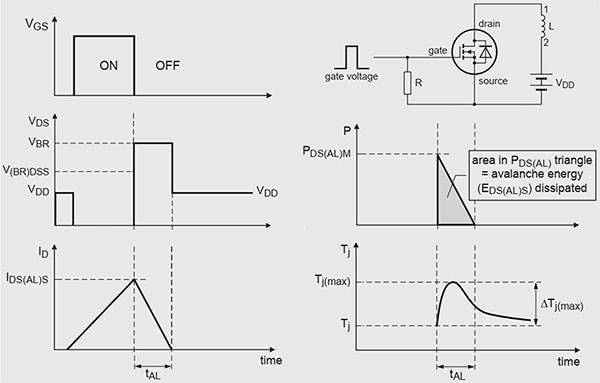

A Figura 4 mostra um controle de bobina simples com um comutador MOSFET e os sinais de tempo antes, durante (janela de tempo tAL) e depois de um único evento de avalanche. Se a quantidade de energia de avalanche dissipada (EDS(AL)S) for muito alta, o calor resultante danificará a estrutura do semicondutor.

Figura 4: Sinais temporais de um MOSFET antes, durante (tAL) e depois de um único evento de avalanche. (Fonte da imagem: Nexperia)

Figura 4: Sinais temporais de um MOSFET antes, durante (tAL) e depois de um único evento de avalanche. (Fonte da imagem: Nexperia)

Os MOSFETs LFPAK56D foram projetados para serem muito robustos e podem suportar vários bilhões de eventos de avalanche sem danos, de acordo com os testes de laboratório da Nexperia. Considerando a energia máxima de avalanche, os estágios acionadores da bobina podem dispensar diodos adicionais de supressão ou limitação e usar apenas a operação de avalanche desses MOSFETs.

Simulação eletrotérmica on-line

Para melhorar a eficiência do sistema, confiar em uma simples Figura de Mérito (FOM), como o produto RDS x QGD, é insuficiente. Em vez disso, os projetistas precisam realizar uma análise de perda mais precisa que leve em conta as perdas resultantes do MOSFET:

- Condutividade da ativação

- Perdas ao ligar e desligar

- Carga e descarga da capacitância de saída

- Perdas de continuidade e comutação do diodo incorporado

- Carga e descarga da capacitância de porta

Para minimizar as perdas totais, os projetistas devem entender a relação entre os parâmetros do MOSFET e o ambiente operacional. Para isso, a Nexperia oferece modelos eletrotérmicos de precisão para MOSFETs que combinam desempenho elétrico e térmico e representam todos os comportamentos importantes do MOSFET. Os desenvolvedores podem usar o simulador on-line PartQuest Explore ou importar os modelos no formato SPICE e VHDL-AMS para a plataforma de simulação de sua preferência.

No momento da redação deste artigo, apenas os modelos elétricos estão disponíveis para os MOSFETs LFPAK56D. Portanto, o exemplo de simulação térmica a seguir trata de um tipo diferente de MOSFET, o BUK7S1R0-40H.

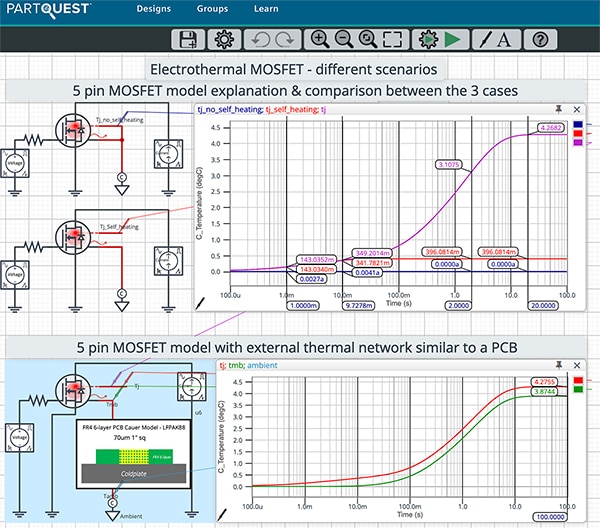

O experimento interativo “IAN50012 Electrothermal models for Power MOSFET” simula três cenários de aquecimento para o MOSFET BUK7S1R0-40H, depois que uma corrente de carga de 36,25 A for ligada. A Figura 5 mostra as três configurações de simulação à esquerda.

Figura 5: é mostrada uma simulação eletrotérmica de um MOSFET usando o simulador on-line PartQuest Explore. (Fonte da imagem: Nexperia)

Figura 5: é mostrada uma simulação eletrotérmica de um MOSFET usando o simulador on-line PartQuest Explore. (Fonte da imagem: Nexperia)

No caso de cima "tj_no_self_heating", a junção e a base de montagem são acopladas diretamente à temperatura ambiente (Tamb) de 0°C sem resistência térmica (Rth). No caso do meio, "tj_self_heating", o chip é acoplado via Rth-j, e Tj aumenta em cerca de 0,4°C. O caso de baixo mostra uma base de montagem (mb) acoplada à temperatura ambiente via Rth_mb de uma placa FR4 de seis camadas com um dissipador de calor. A Tmb (verde) aumenta para 3,9°C e a Tj (vermelha) aumenta para 4,3°C.

Conclusão

Os MOSFETs LFPAK56D de perda baixíssima proporcionam excelente eficiência e densidade de potência em conversores de comutação rápida ou acionadores de motor. As considerações de projeto elétrico e térmico da PCI e a simulação eletrotérmica discutidas aqui ilustram como os projetistas podem superar os desafios de projetos robustos, altamente eficientes e com restrições de espaço.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.