Crie rapidamente clocks de alta frequência e baixo jitter usando um módulo de malha de tradução

Contributed By DigiKey's North American Editors

2021-08-04

Os projetistas de sistemas de instrumentação e medição precisam de sinais com pouca variação de atraso (jitter), sem espúrio, a fim de fornecer as relações sinal-ruído (SNRs) ou magnitudes vetoriais de erro (EVMs) necessárias para atender às demandas cada vez mais exigentes dos clientes. Ao mesmo tempo, eles também estão enfrentando uma pressão significativa para reduzir a pegada das placas, bem como o custo e a complexidade do projeto. Este último é fundamental para encurtar o tempo de desenvolvimento e atender aos prazos mais curtos para colocação no mercado.

Para enfrentar os muitos desafios de aplicação, os engenheiros precisam fazer a transição de suas soluções de instrumentação e clocks de medição a partir de projetos feitos sob medida, tradicionalmente discretos, para soluções mais integradas. Um passo importante para isso é utilizar uma malha de captura de fase (PLL) translacional integrada. Isto permite a conversão de frequência de um sinal do oscilador tradicional controlado por tensão (VCO), enquanto mantém substancialmente o jitter e ruído de fase de um oscilador local externo fixo (LO).

Este artigo discute o papel das malhas de tradução para alcançar o menor ruído de fase integrado da indústria. A título de exemplo, ele introduz o sistema no pacote da malha de tradução (TL SiP) ADF4401A da Analog Devices e mostra como ele atende aos requisitos de desempenho através de um sinal de saída com capacidade de jitter integrada a banda larga abaixo de 10 femtosegundos (fs) rms e melhor isolação para atenuar componentes espúrios, como também cumpre com necessidades de integração, custo, complexidade e tempo de colocação no mercado dos projetistas.

PLL tradicional vs. operações de malha de tradução

O objetivo principal de uma malha de tradução é gerar um sinal de saída bloqueado a um sinal de referência de entrada com ruído de fase na banda significativamente reduzido em comparação com os PLLs tradicionais.

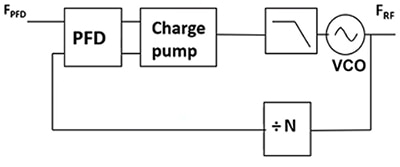

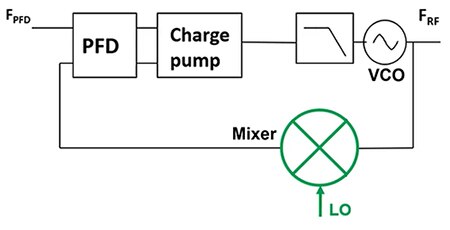

Um PLL padrão consiste de um sistema de realimentação contendo um detector de frequência-fase (PFD), bomba de carga, filtro de passa-baixa (LPF), VCO e um divisor N da frequência de realimentação (Figura 1).

Figura 1: O PLL padrão trava a uma referência de frequência mais baixa (FPFD) e gera uma frequência de saída (FRF). (Fonte da imagem: Bonnie Baker)

Figura 1: O PLL padrão trava a uma referência de frequência mais baixa (FPFD) e gera uma frequência de saída (FRF). (Fonte da imagem: Bonnie Baker)

A PFD compara a fase da referência de entrada e a fase do sinal de realimentação e gera uma série de pulsos proporcionais ao erro de fase entre eles. A bomba de carga recebe os pulsos PFD e os converte em fonte de corrente ou pulsos de dreno que, por sua vez, sintonizam o VCO tanto para cima como para baixo na frequência. O LPF remove toda a energia de alta frequência dos pulsos e os converte em uma tensão que o VCO pode utilizar. O sinal de saída do VCO é alimentado de volta ao bloco PFD através do divisor N para completar a malha.

A função de transferência de frequência da Figura 1 é calculada usando a Equação 1:

![]() Equação 1

Equação 1

Onde FRF é a frequência de saída

N é a relação do divisor de realimentação (pode ser inteira ou fracionária)

FPFD é a frequência da PFD

A base de ruído na banda da Figura 1 é calculada usando a Equação 2:

![]() Equação 2

Equação 2

Onde FOMPLL é a figura de mérito (FOM) da base de ruído de fase na banda da PLL

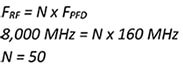

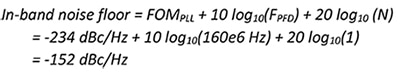

Considere um exemplo com uma FOM da base de ruído de fase na banda de -234 decibéis por Hertz (dB/Hz); uma frequência (FPFD) de 160 megahertz (MHz), e uma frequência de saída (FRF) de 8 gigahertz (GHz).

Para este sistema, a Equação 1 é usada para calcular o valor de N:

A equação 2 é usada para calcular a base de ruído na banda:

No cálculo acima, o divisor N contribui fortemente para a base geral de ruído na banda, com 20 log10 (50), o que equivale a 34 dB. Um valor menor de N diminuiria a base de ruído na banda; no entanto, também diminuiria a frequência de saída. Então, como gerar uma alta frequência de saída e manter um ganho (N) de malha inferior?

Figura 2: Para uma PLL padrão neste exemplo, o ruído oriundo do divisor de realimentação (20 log10(N)) tem um ruído na banda maior de 34 dB em comparação com a parcela amarela menor onde N = 1. (Fonte da imagem: Bonnie Baker)

Figura 2: Para uma PLL padrão neste exemplo, o ruído oriundo do divisor de realimentação (20 log10(N)) tem um ruído na banda maior de 34 dB em comparação com a parcela amarela menor onde N = 1. (Fonte da imagem: Bonnie Baker)

A solução para esta questão é substituir o divisor N por um estágio de mistura de baixa conversão (Figura 3).

Figura 3: Uma malha de tradução usa um misturador para baixar a frequência VCO até a frequência PFD em vez de usar um divisor de realimentação tradicional. (Fonte da imagem: Bonnie Baker)

Figura 3: Uma malha de tradução usa um misturador para baixar a frequência VCO até a frequência PFD em vez de usar um divisor de realimentação tradicional. (Fonte da imagem: Bonnie Baker)

Na Figura 3, o misturador substitui o divisor de realimentação N, resultando em um ganho de malha igual a 1 (N=1). Esta operação diminuirá muito a contribuição da malha de realimentação para a base de ruído na banda. Para o cálculo do ruído na banda, o valor de N é agora igual a 1. Usando a Equação 2, a base de ruído na banda para o sistema modificado é o seguinte:

O novo ruído na banda mostra uma melhoria de 34 dBc/Hz.

Na Figura 3, o misturador depende de um LO de ruído extremamente baixo, chamado LO de compensação ou LO Offset. FLO ± FRF deve ser igual a FPFD para conseguir o bloqueio.

Com a arquitetura da malha de tradução, o ruído de fase do LO Offset é muito importante para se obter o melhor desempenho na saída de RF. Por esta razão, os engenheiros normalmente projetariam um LO Offset baseado em ondas acústicas de superfície controlada por tensão (SAW), ou osciladores (VCSOs), ou geradores de pente ou osciladores de ressonância dielétrica (DROs). NOTA: Para suporte com o projeto de um LO Offset, contate a Analog Devices.

Desafios da malha de tradução

Tradicionalmente, o projeto de uma malha de tradução de baixo ruído envolve a implementação de numerosos blocos de circuito, resultando em um projeto complexo, geralmente grande, e com flexibilidade limitada. Além disso, todo o circuito deve ser validado e caracterizado para a operação destinada. Por exemplo, uma grande preocupação de projeto é a fuga de LO (isolação de LO a RF) para o sinal de saída de RF. Este é um desafio significativo a ser enfrentado pelos engenheiros. Com projetos tradicionais, os engenheiros normalmente procedem a múltiplas iterações de projeto para obter um desempenho otimizado e uma isolação adequada.

A Figura 3 mostra como o ADF4401A integra grandes blocos de circuito para fornecer uma solução totalmente caracterizada e elimina as áreas tradicionalmente difíceis relacionadas ao desempenho e à isolação em projetos de malha de tradução. Esta solução programável permite que os engenheiros obtenham um desempenho otimizado no primeiro esforço e reduzam o tempo de colocação no mercado.

Avaliando o ADF4401A

O ADF4401A foi projetado para ajudar os engenheiros a reduzir o tempo de colocação de instrumentos de alto desempenho no mercado, utilizando uma solução de geração de frequência com uma largura de banda de RF de 62,5 MHz a 8 GHz. Usando um misturador de baixa conversão, o ADF4401A tem um ruído muito baixo na banda com um jitter de banda larga de ~9 femtosegundos (fs) integrado de 100 Hz a 100 MHz. As técnicas de projeto e layout dentro do ADF4401A permitem uma típica faixa dinâmica livre de espúrios de 90 dBc. Um tamanho de invólucro de 18 x 18 x 2,018 milímetros (mm) reduz substancialmente o espaço da placa em comparação com um projeto tradicional discreto.

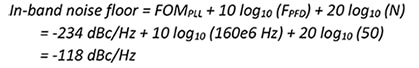

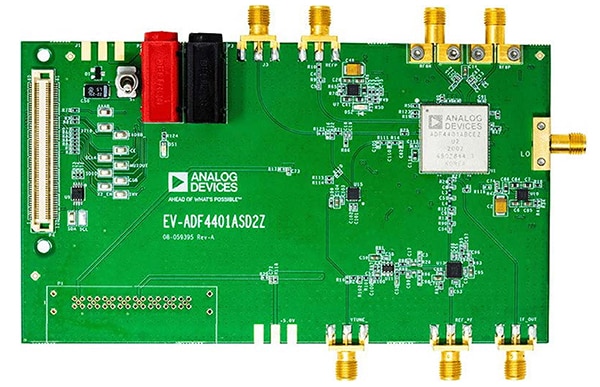

Para avaliar o desempenho do dispositivo, os projetistas podem usar a placa de avaliação EV-ADF4401ASD2Z (Figura 4). A placa inclui uma malha de tradução completa, incluindo um PFD externo (HMC3716), um filtro ativo (LT6200) e um multiplexador (ADG1609).

Figura 4: A placa de avaliação EV-ADF4401ASD2Z para o módulo da malha de tradução ADF4401A inclui um PFD externo, uma interface USB e reguladores de tensão. (Fonte da imagem: Analog Devices)

Figura 4: A placa de avaliação EV-ADF4401ASD2Z para o módulo da malha de tradução ADF4401A inclui um PFD externo, uma interface USB e reguladores de tensão. (Fonte da imagem: Analog Devices)

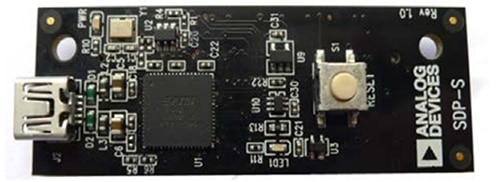

O EV-ADF4401ASD2Z inclui o ADF4401A TL SiP com VCO integrado, um filtro de malha (5 MHz), um PFD, uma interface USB e reguladores de tensão. Além disso, o EV-ADF4401ASD2Z requer a placa controladora (serial) da plataforma de demonstração do sistema (SDP) EVAL-SDP-CS1Z (SDP-S) (Figura 5). A placa fornece uma conexão USB a partir de um PC à EV-ADF4401ASD2Z para que ela possa ser programada. A placa controladora não é fornecida no kit EV-ADF4401ASD2Z.

Figura 5: A placa controladora EVAL-SDP-CS1Z (ou SDP-S) é necessária para fornecer uma conexão USB do EV-ADF4401ASD2Z a um PC para programação. (Fonte da imagem: Analog Devices)

Figura 5: A placa controladora EVAL-SDP-CS1Z (ou SDP-S) é necessária para fornecer uma conexão USB do EV-ADF4401ASD2Z a um PC para programação. (Fonte da imagem: Analog Devices)

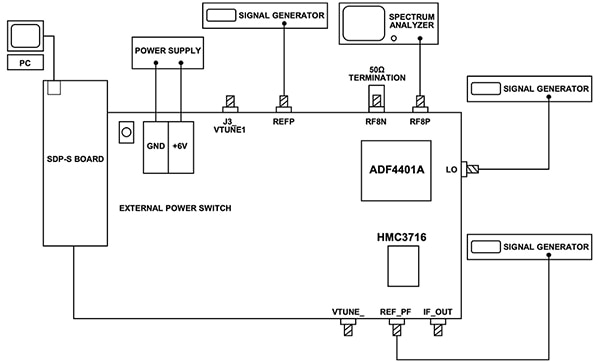

A figura 6 mapeia as conexões físicas do sistema EV-ADF4401ASD2Z. O software associado Analysis | Control | Evaluation (ACE) controla as funções TL SiP. A energia é derivada de uma fonte de alimentação de 6 volts aplicada externamente.

Figura 6: Um diagrama de configuração EV-ADF4401ASD2Z mostra o equipamento e as conexões necessárias para avaliar o ADF4401A, incluindo a placa de controle SDP-S, PC, fonte de alimentação, geradores de sinais e analisador de espectro. (Fonte da imagem: Analog Devices)

Figura 6: Um diagrama de configuração EV-ADF4401ASD2Z mostra o equipamento e as conexões necessárias para avaliar o ADF4401A, incluindo a placa de controle SDP-S, PC, fonte de alimentação, geradores de sinais e analisador de espectro. (Fonte da imagem: Analog Devices)

O equipamento sugerido para usar com esta placa de avaliação inclui um PC Windows, um analisador de espectro ou um analisador de fonte de sinal, e três geradores de sinal.

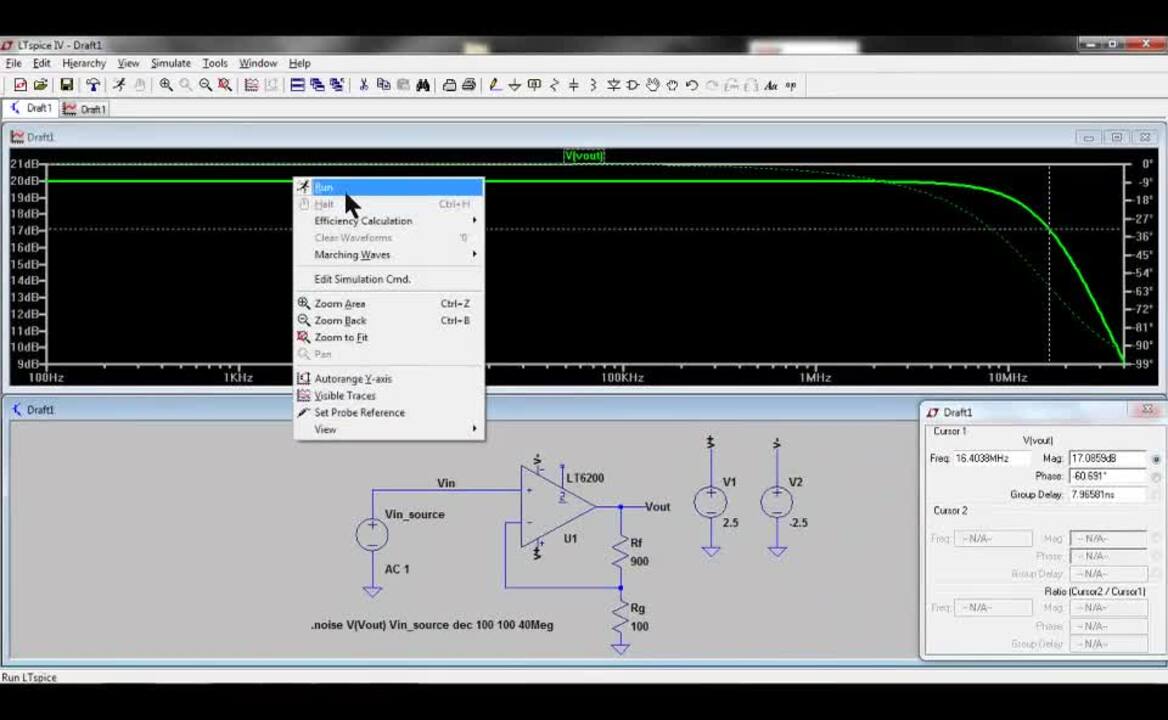

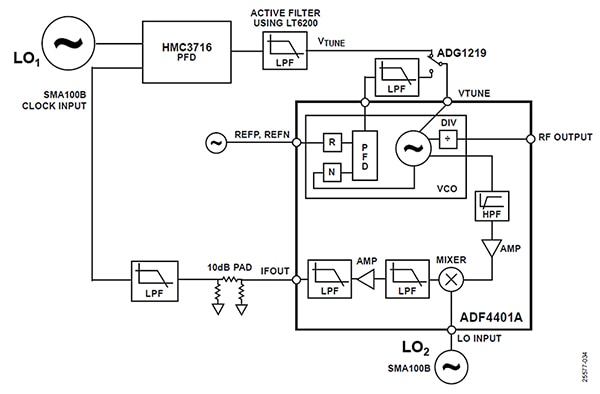

O diagrama de blocos do EV-ADF4401ASD2Z mostra o módulo ADF4401A, juntamente com o PFD HMC3716 da Analog Devices, o amp-op LT6200 e o interruptor SPDT ADG1219 (Figura 7).

Figura 7: O diagrama de blocos da placa de avaliação EV-ADF4401ASD2Z mostra os principais componentes que suportam a malha de tradução AD4401A. (Fonte da imagem: Analog Devices)

Figura 7: O diagrama de blocos da placa de avaliação EV-ADF4401ASD2Z mostra os principais componentes que suportam a malha de tradução AD4401A. (Fonte da imagem: Analog Devices)

É vital usar um PFD que possa operar em altas frequências, pois isso minimiza a necessidade de divisores, o que pode degradar a resposta de ruído na banda. A capacidade de comparação de frequência e fase a 1,3 GHz do HMC3716 da Analog Devices o torna ideal para uso na faixa IF do ADF4401A. A capacidade de tal circuito de comparar tanto a frequência quanto a fase elimina a necessidade de circuitos adicionais para direcionar a frequência para a frequência de saída pretendida. O HMC3716 se torna o PFD externo para completar a malha de offset. A faixa de operação de alta frequência e a base de ruído de fase ultrabaixa do HMC3716 tornam possível o projeto de filtros de malha de grande largura de banda.

Na Figura 7, o amp-op LT6200 com uma configuração LPF atenua os espúrios de alta frequência, enquanto o interruptor ADG1219 completa a malha de tradução do sistema.

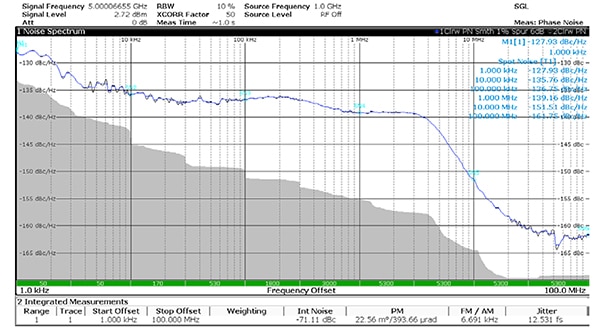

O dispositivo de avaliação EV-ADF4401ASD2Z cria parcelas de ruído na banda e medições de jitter como mostrado na Figura 8.

Figura 8: Ruído de fase de banda lateral única na saída de 5 GHz, com uma referência externa HMC3716 de 500 MHz e LO externa em 4,5 GHz. (Fonte da imagem: Analog Devices)

Figura 8: Ruído de fase de banda lateral única na saída de 5 GHz, com uma referência externa HMC3716 de 500 MHz e LO externa em 4,5 GHz. (Fonte da imagem: Analog Devices)

Na Figura 8, a entrada LO2 e HMC3716 é um gerador de sinais de RF e microondas SMA100B. O ruído na banda de LO2 da placa de avaliação é de aproximadamente -135 dBc/Hz, o que é aparente em baixos offsets de até 300 kHz. O módulo ADF4401A, LO2, HMC3716 PFD e o filtro de malha contribuem para um ruído na banda de cerca de -140 dBc/Hz. O ruído interno de fase aparece entre 5 MHz e 50 MHz, e a base do ruído de fase do dispositivo é de aproximadamente -160 dBc/Hz. Estes juntos dão um jitter rms de 12,53 fs no total.

Conclusão

Os sistemas de instrumentação de alta velocidade exigem clocks de jitter baixíssimos para garantir que os dados de saída não sejam comprometidos. O desafio para os engenheiros é encontrar dispositivos adequados que possam construir o sistema de clock de alta velocidade em gigahertz. A malha de tradução ADF4401A simplifica muito a seleção do dispositivo para construir o sistema de clock, fornecendo um módulo compacto que garante baixo jitter em frequências mais altas, ao mesmo tempo em que reduz o espaço da placa, o custo e o tempo de colocação no mercado.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.