Aproveite as vantagens da I3C para uma comunicação mais rápida, simples e flexível entre CIs

Contributed By DigiKey's North American Editors

2024-12-17

As interfaces seriais na placa para comunicações entre circuitos integrados (CI) são dominadas pelo Circuito Interintegrado (I²C) e pela Interface Periférica Serial (SPI), que estão disponíveis desde a década de 1980. Essas interfaces são amplamente usadas para conectar sensores e CIs de baixa velocidade a unidades de microcontroladores (MCUs) para comunicação intraplaca em distâncias curtas. Entretanto, à medida que os sistemas digitais ficam mais rápidos, essas interfaces, limitadas a taxas de dados típicas de 1 megabit por segundo (Mbit/s) para I²C e 10 Mbits/s para SPI, tornaram-se um fator limitante. Outras limitações, incluindo interrupção dedicada ou linhas de habilitação de chip, exigem conexões de sinal adicionais, aumentando o número de fios e a complexidade das conexões de barramento.

O barramento de Circuito Interintegrado Aprimorado (I3C) destina-se a modernizar as comunicações entre os interintegrados. Ele oferece taxas de dados mais altas, maior flexibilidade e uma verdadeira interface de dois fios com interrupções na banda (IBIs) em vez de interrupções externas.

Este artigo discute as características da interface I3C e por que ela pode ser uma boa modernização das interfaces seriais I²C e SPI. Dispositivos típicos de MCU, comutação de CI e sensores serão usados para mostrar sua aplicação.

Barramentos de comunicação incorporados

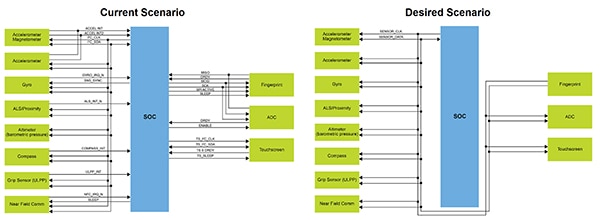

As interconexões seriais incorporadas, como I²C e SPI, têm sido empregadas há muitos anos para comunicações dentro da placa. Elas são usadas principalmente como barramentos de comunicação entre sensores e dispositivos de interface do usuário e seus processadores de controle. O número de sensores em sistemas típicos aumentou para dez a vinte em um telefone e para um número significativamente maior em veículos. Ao mesmo tempo, os requisitos de comunicação se tornaram mais desafiadores para os projetistas à medida que aumenta a demanda por maior velocidade, menor consumo de energia e menos condutores. Os projetistas devem atender a essas demandas e, ao mesmo tempo, manter o controle do processador por meio de interrupções e linhas de habilitação (Figura 1).

Figura 1: As comunicações incorporadas devem suportar velocidades mais altas, menor consumo de energia e um número mínimo de fios. (Fonte da imagem: NXP Semiconductors)

Figura 1: As comunicações incorporadas devem suportar velocidades mais altas, menor consumo de energia e um número mínimo de fios. (Fonte da imagem: NXP Semiconductors)

A tecnologia atual implementa a interface do sensor e do dispositivo de controle do usuário usando interfaces I²C de dois fios ou SPI de quatro fios. As linhas de interrupção, habilitação e outras linhas de controle são separadas das linhas de clock e de dados, resultando em mais linhas por interface.

Os projetistas precisam de uma abordagem de interface mais voltada para o futuro, que elimine esses condutores extras das interconexões e manipule essas operações na banda, usando apenas o clock e as linhas de dados. Além disso, o barramento deve ser capaz de operar em velocidades mais altas e com menos perdas de energia.

Interface I3C

A I3C foi desenvolvida pela Mobile Industry Processor Interface (MIPI) Alliance para atender a esses requisitos. A interface está disponível como MIPI I3C para membros da MIPI e como MIPI I3C Basic com funcionalidade reduzida para não membros. Como as interfaces I²C e SPI antigas, a forma aprimorada é serial e é implementada usando dois fios para minimizar a quantidade de pinos e o número de caminhos de sinal entre os componentes. Ela tem uma taxa de dados de até 12,5 Mbits/s com um clock de 12,5 megahertz (MHz), usando o modo de taxa de dados única (SDR). Opera em níveis de energia mais baixos e usa uma arquitetura de projeto simples, porém flexível.

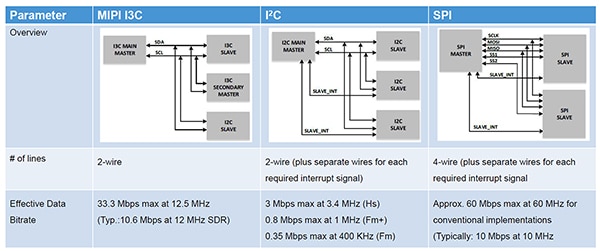

Notavelmente, o padrão I3C mantém uma retrocompatibilidade limitada com o sistema I²C, permitindo que os dispositivos I²C existentes sejam conectados ao barramento I3C e, ao mesmo tempo, permitindo que o barramento alterne para taxas de dados mais altas para comunicação entre dispositivos I3C compatíveis. Uma comparação das configurações do sistema é mostrada na Figura 2.

Figura 2: A comparação das configurações básicas das interfaces I3C, I²C e SPI mostra que a I3C tem maior velocidade e fiação mais simples. (Fonte da imagem: NXP Semiconductors)

Figura 2: A comparação das configurações básicas das interfaces I3C, I²C e SPI mostra que a I3C tem maior velocidade e fiação mais simples. (Fonte da imagem: NXP Semiconductors)

A interface SPI de quatro fios pode operar mais rapidamente e suporta comunicação full-duplex. A I²C se comunica usando half-duplex em um barramento de dois fios que consiste em um clock (SCL) e linhas de dados (SDA). Ambas exigem linhas extras para suportar interrupções e outras funções de controle, como a seleção de chip. A I3C reduz para dois fios usados na interface, eliminando as linhas separadas de interrupção, habilitação e seleção de chip, usadas no I²C e no SPI. Essa redução no número de fios é uma vantagem significativa em um sistema que requer de dez a vinte sensores individuais ligados ao processador, cada um com vários fios secundários. As interrupções e outras linhas de controle são substituídas por IBIs. Nesse método, um sensor ou dispositivo de destino impõe seu endereço na barra de pinos do barramento I3C para notificar o processador sobre uma interrupção.

A diferença nas taxas de clock entre I²C e I3C é significativa. A I²C geralmente tem clock de 100 quilohertz (kHz), 400 kHz ou 1 MHz, enquanto a I3C pode ter clock de 12,5 MHz. Anteriormente, a SPI era usada para taxas de clock superiores a 1 MHz. A seleção do projeto foi feita entre a taxa de clock e o número de fios. A I3C mudou isso, oferecendo taxas de clock e de dados mais altas, usando uma topologia verdadeira de dois fios.

As saídas push-pull, que podem comutar mais rapidamente do que os acionadores de dreno ou coletor aberto, contribuem significativamente para o aumento da taxa de clock da I3C. Para manter a compatibilidade com os dispositivos I²C, a I3C pode alternar entre acionadores de dreno aberto e push-pull, dependendo do estado do barramento. O projeto de coletor ou dreno aberto é usado durante o endereçamento inicial, ou arbitragem, em que os dispositivos I²C e I3C podem estar na linha simultaneamente. A I3C usa push-pull quando a comunicação é unidirecional, e não há chance de um dispositivo I²C se comunicar simultaneamente.

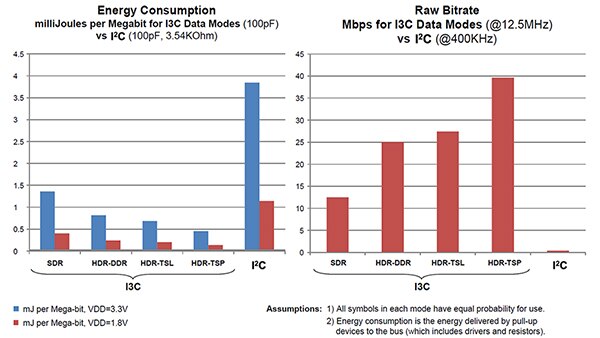

Além da SDR padrão, a I3C oferece suporte a vários modos opcionais de alta taxa de dados (HDR). Esses modos HDR operam com a mesma taxa de clock, mas transmitem com uma densidade de dados maior. O primeiro dos modos HDR é a taxa de dados dupla HDR (HDR-DDR), em que os dados são sincronizados em ambas as bordas do sinal de clock, proporcionando quase duas vezes a taxa de dados. Para um clock de 12,5 MHz, o modo DDR atinge uma taxa de dados efetiva de 20 Mbits/s.

Os símbolos ternários HDR têm duas versões: Símbolo ternário HDR, puro (HDR-TSP) somente para dispositivos I3C e símbolo ternário HDR, antigo (HDR-TSL) para barramentos que incluem dispositivos I²C e I3C. Os modos de símbolo ternário atingem três bits de dados por clock usando símbolos de três bits (ternários) codificados nas linhas SCL e SDA.

O modo de transporte em massa HDR (HDR-BT) oferece os dados mais altos, suportando comunicações em linhas de dados SDA quádruplas, duplas ou simples. Isso resulta em oito, quatro ou duas vezes o desempenho bruto da taxa de dados única na mesma taxa de clock.

Esses aumentos na velocidade de transferência de dados permitem que os dispositivos sejam ligados por um período mais curto, reduzindo o ciclo de trabalho de energia do barramento. Isso reduz o consumo de energia em comparação com a I²C (Figura 3). A mudança de acionadores de coletor aberto com resistores de pull-up externos para acionadores push-pull reduz ainda mais o consumo de energia, pois os resistores de pull-up requerem energia significativa para operar.

Figura 3: A I3C oferece melhorias na taxa de dados e no consumo de energia em comparação com a I²C. (Fonte da imagem: NXP Semiconductors)

Figura 3: A I3C oferece melhorias na taxa de dados e no consumo de energia em comparação com a I²C. (Fonte da imagem: NXP Semiconductors)

Endereçamento

A I²C usa endereços estáticos de 7 ou 10 bits para cada dispositivo de barramento. Isso foi alterado na I3C para endereçamento dinâmico de 7 bits, em que o mestre do barramento define o endereço do dispositivo durante a atribuição dinâmica de endereço (DAA) e o armazena em um registrador do dispositivo. O endereçamento estático, como no caso de um periférico I²C, ainda pode ser usado na I3C.

Devido ao endereçamento dinâmico, os endereços dos dispositivos podem ser alterados posteriormente. Isso oferece suporte à adição dinâmica, que permite que um novo dispositivo seja adicionado ao barramento enquanto ele opera. O novo dispositivo, conectado ao barramento I3C, sinaliza sua presença para o mestre I3C enviando uma solicitação de adição dinâmica. O controlador mestre confirma a solicitação e atribui um endereço para adicionar o dispositivo ao barramento.

IBIs

I3C é um verdadeiro barramento de dois fios que usa IBIs, em vez de linhas de interrupção dedicadas, como I²C. As IBIs ocorrem quando um dispositivo de destino sinaliza sua disponibilidade para o mestre, diminuindo o potencial da linha SDA. Em seguida, o mestre inicia o clock na linha SCL, e o dispositivo de destino transmite seu endereço para o barramento I3C para notificar o controlador sobre uma interrupção.

Códigos de comando comuns

Os códigos de comando comuns (CCC) são comandos padronizados que o controlador pode enviar como uma transmissão geral para todos os dispositivos I3C simultaneamente ou para um dispositivo de destino específico. Esses comandos são para itens relacionados ao gerenciamento do barramento. O formato do protocolo CCC começa com o endereço de transmissão I3C, que é reconhecido por todos os dispositivos I3C no barramento. Qualquer dispositivo I²C no barramento não reconhecerá a solicitação, pois esse é um endereço I²C reservado.

Cada comando inclui um campo de ID de descritor de 8 bits e pode ser seguido por uma carga útil de comando. Um comando enviado a um dispositivo específico passa o endereço do dispositivo no primeiro byte da carga útil. Há mais de quarenta comandos CCC, incluindo:

- Inserir atribuição dinâmica de endereço (ENTDAA)

- Definir nova atribuição dinâmica de endereço (SETNEWDA)

- Ativar eventos (ENEC)/Desativar eventos (DISEC)

- Redefinição da atribuição dinâmica de endereços (RSTDAA)

- Entrar no modo de alta taxa de dados (ENTHDRx)

- Obter registrador de características do dispositivo (GETDCR)

Os fornecedores têm direito a uma gama dedicada de IDs CCC para implementar seus próprios comandos.

Detecção e recuperação de erros

Ao contrário da I²C, a I3C inclui provisões para detecção e recuperação de erros. Seis métodos de erro e recuperação para dispositivos de destino são obrigatórios, e outro é opcional. Métodos adicionais de erro e recuperação também estão disponíveis especificamente para erros do mestre.

Componentes suportados pela I3C

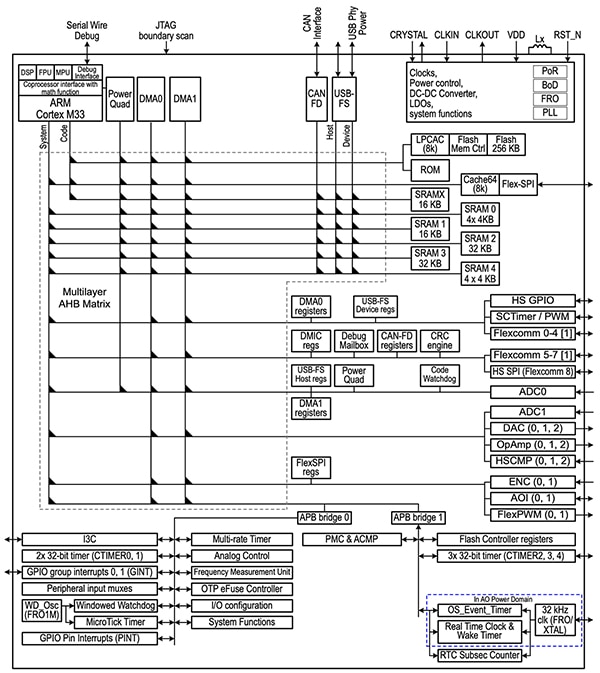

Conforme mostrado na Figura 2 (à esquerda), uma rede I3C básica compreende pelo menos um controlador mestre e um ou mais destinos, ou escravos I3C. O mestre principal pode ser uma MCU, como a LPC5534JHI48-00MP da NXP Semiconductors (Figura 4). É uma MCU Arm® Cortex®-M33 de 32 bits com 128 quilobytes (Kbytes) de SRAM e 256 Kbytes de Flash. Sua interface Flexcomm suporta oito interfaces seriais diferentes, incluindo I3C.

Figura 4: A MCU LPC5534JHI48/00MP inclui uma interface I3C e sete outras interfaces seriais. (Fonte da imagem: NXP Semiconductor)

Figura 4: A MCU LPC5534JHI48/00MP inclui uma interface I3C e sete outras interfaces seriais. (Fonte da imagem: NXP Semiconductor)

O barramento I3C permite a adição de mestres secundários introduzidos no barramento como escravos. Também pode ter vários mestres, mas somente um pode ser o controlador. Uma vez inscrito, o mestre secundário pode solicitar o status de mestre atual e, se o mestre atual aceitar, seu controle será transferido para o mestre secundário solicitante.

Um sensor I3C típico é o P3T2030CUKAZ da NXP. Esse sensor de temperatura converte temperaturas de -40°C a +125°C em um valor digital de 12 bits com uma precisão de ±2°C. Ele inclui uma interface serial I²C e I3C no modo SDR.

Um sensor mais sofisticado é o giroscópio e acelerômetro de sistemas microeletromecânicos (MEMS) de três eixos ICM-42605 da TDK InvenSense. Como um giroscópio de taxa, ele mede taxas de rotação de ±15,2 a ±2000 graus por segundo (°/s). Sua faixa como acelerômetro é de ±2 a ±15 g. Ele detecta movimento, inclinação, toque ou passos (pedômetro). Como um sensor I3C, ele opera a 12,5 MHz no modo SDR e a 25 MHz no modo DDR.

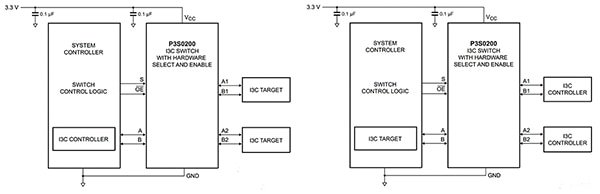

Os CIs, como o comutador I3C P3S0200GMX da NXP, podem reconfigurar o barramento I3C encaminhando os sinais do barramento I3C entre um controlador I3C e vários conjuntos de dispositivos de destino, ou entre um único destino e vários controladores I3C, conforme determinado por uma MCU externa (Figura 5).

Figura 5: O comutador I3C P3S0200GMX pode ser usado para reconfigurar um barramento I3C roteando os sinais do barramento I3C entre um controlador I3C e vários conjuntos de dispositivos de destino, ou entre um único destino e vários controladores I3C. (Fonte da imagem: NXP Semiconductors)

Figura 5: O comutador I3C P3S0200GMX pode ser usado para reconfigurar um barramento I3C roteando os sinais do barramento I3C entre um controlador I3C e vários conjuntos de dispositivos de destino, ou entre um único destino e vários controladores I3C. (Fonte da imagem: NXP Semiconductors)

A alternância entre dois destinos pode ser necessária se ambos os destinos tiverem o mesmo endereço e não puderem residir no mesmo barramento. Como alternativa, um único destino pode ter que ser compartilhado entre dois processos, exigindo uma alternância entre os dois controladores I3C.

Conclusão

A I3C é uma interface serial que prolonga o barramento I²C, aumentando sua taxa de dados, reduzindo o número de fios e adicionando flexibilidade ao controle do barramento. É um aprimoramento que amplia a utilidade das interfaces I²C e SPI antigas.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.