Os fundamentos dos sintetizadores de frequência de malha de captura de fase

Contributed By DigiKey's North American Editors

2021-02-03

O aumento das taxas de dados em barramentos de comunicações seriais de alta velocidade requer clocks de sistema com frequências mais elevadas, estabilidade superior, maior resolução de frequência e maior pureza de sinal. Os sintetizadores digitais diretos oferecem essas características, mas somente em frequências abaixo de 2 ou 3 gigahertz (GHz). É necessária uma solução para frequências até dezenas de gigahertz.

Essa solução começa com sintetizadores de frequência analógicos baseados em malha de captura de fase (PLL) que geram frequências de clock de até 30 GHz. Em seguida, os sintetizadores N inteiros (que multiplicam a frequência de referência por um valor inteiro) e os sintetizadores N fracionários (que multiplicam a frequência de referência por valores fracionários não inteiros) empregam técnicas especiais que minimizam o ruído de fase e impurezas de sinal semelhantes.

O arquivo descreve o projeto tanto de sintetizadores de frequência N inteiros quanto de fracionários usando modelos de dispositivos da Analog Devices. O artigo também destaca as inovações que permitem que esses dispositivos sejam usados para links de dados seriais de alta velocidade, bem como para radares ágeis de frequência.

Sintetizadores de malha de captura de fase N inteiros

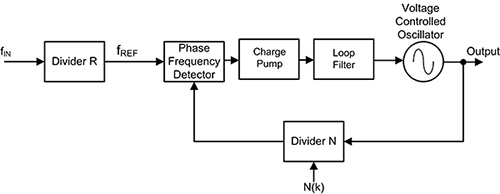

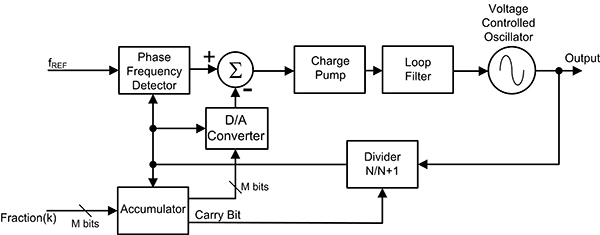

Os circuitos PLL são utilizados para controle de frequência e fase. Podem ser configurados como fontes de clock, multiplicadores de frequência, demoduladores, geradores de rastreamento ou circuitos de recuperação de clock. Cada uma dessas aplicações exige características diferentes, mas todas utilizam o mesmo conceito básico de circuito. A Figura 1 mostra um diagrama de blocos de uma PLL básica configurada como multiplicador de frequência.

Figura 1: diagrama de blocos de um sintetizador de frequência de malha de captura de fase de N inteiro clássico. (Fonte da imagem: DigiKey)

Figura 1: diagrama de blocos de um sintetizador de frequência de malha de captura de fase de N inteiro clássico. (Fonte da imagem: DigiKey)

O funcionamento desse circuito é típico de todas as malhas de captura de fase. Trata-se basicamente de um sistema de controle de realimentação que controla a fase de um oscilador controlado por tensão (VCO). O sinal de entrada é aplicado a um divisor de pré-escala, que divide a frequência de entrada por um fator R. A saída do pré-escalador é a frequência de referência, que forma uma entrada de um detector de frequência e fase (PFD).

A outra entrada do PFD é um sinal de realimentação da saída de um contador de divisão por N. Normalmente, se a PLL estiver bloqueada, as frequências de ambos os sinais serão praticamente as mesmas. A saída do detector de fase é uma tensão proporcional à diferença de fase entre as duas entradas. Se a malha estiver desbloqueada, como acontece na partida ou se existir um grande deslocamento instantâneo na frequência da entrada, o detector de frequência e fase funciona para conduzir a frequência de operação da PLL para o ajuste desejado. Quando essa frequência é atingida, o PFD retorna ao modo de detector de fase e tem uma saída proporcional à diferença de fase entre a frequência de referência e o sinal de realimentação.

O detector de frequência e fase aciona uma bomba de carga, que é uma fonte de corrente chaveada bipolar. Isso significa que ele pode emitir pulsos de corrente positivos e negativos para o filtro de malha da PLL.

O filtro de malha suaviza o sinal de erro de fase e também determina as características dinâmicas da PLL. O sinal filtrado controla o VCO. Note que a saída do VCO é uma frequência que é N vezes a entrada fornecida à entrada de referência de frequência para o detector de frequência e fase e é N/R vezes a entrada de frequência. Esse sinal de saída é enviado de volta para o detector de fase pelo contador de divisão por N.

Normalmente, o filtro de malha é projetado para corresponder às características exigidas pela aplicação da PLL. Se a PLL for receber e rastrear um sinal, a largura de banda do filtro de malha será maior do que se estivesse esperando uma frequência de entrada fixa. A faixa de frequência que a PLL aceitará e travará é chamada de "faixa de captura". Assim que a PLL estiver travada e rastreando um sinal, a faixa de frequências que ela seguirá é chamada de "faixa de rastreamento". Geralmente, a faixa de rastreamento é maior que a faixa de captura. O filtro de malha da PLL também determina a velocidade com que a frequência do sinal pode mudar e ainda assim manter travada, ou seja, a taxa de inclinação máxima. Quanto mais estreita for a largura de banda do filtro de malha, menor será o erro de fase atingível. Isso é feito à custa de uma resposta mais lenta e de uma faixa de captura reduzida. As PLLs utilizadas em aplicações de clock funcionam principalmente com frequências fixas. Em geral, a largura de banda do filtro de malha deve ser muito inferior à frequência de referência.

Visto que a frequência de saída PLL é um número inteiro múltiplo da frequência de referência, sua resolução de frequência é igual à frequência de referência. A obtenção de uma resolução de frequência mais precisa requer a diminuição da frequência de referência, o que é feito com o contador de pré-escala R.

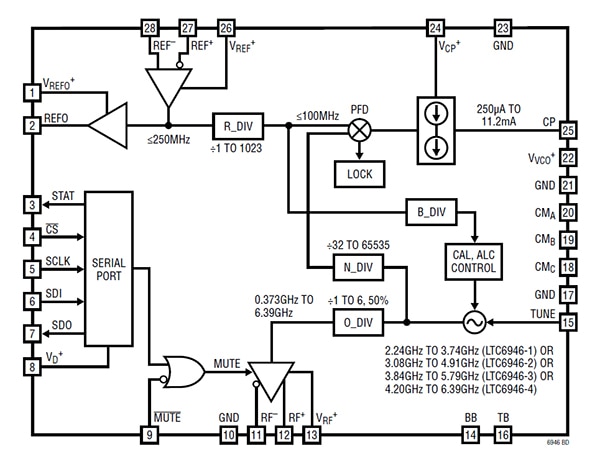

Um exemplo comercial de um sintetizador de frequência de N inteiro é o LTC6946IUFD-3#PBF, da Analog Devices, um sintetizador de baixo ruído de 0,64 a 5,790 GHz com um VCO integrado e excelente desempenho contra espúrios (Figura 2). É membro de uma família de quatro CIs sintetizadores, cada um com uma faixa de frequência diferente, abrangendo uma faixa total de 0,373 a 6,390 GHz.

Figura 2: diagrama de blocos do sintetizador de frequência de N inteiro LTC6946IUFD-3#PBF da Analog Devices com VCO integrado. (Fonte da imagem: Analog Devices)

Figura 2: diagrama de blocos do sintetizador de frequência de N inteiro LTC6946IUFD-3#PBF da Analog Devices com VCO integrado. (Fonte da imagem: Analog Devices)

Esse sintetizador requer um filtro de malha externo fornecido pelo usuário, que pode ser otimizado para a aplicação específica. Existe um divisor do contador interno de pré-escala com uma faixa de divisão de 1 a 1023. O divisor de malha tem uma faixa de 32 a 65535. A corrente da bomba de carga é ajustável de 250 microamperes (mA) a 11,2 miliamperes (mA) para corresponder aos requisitos do filtro de malha.

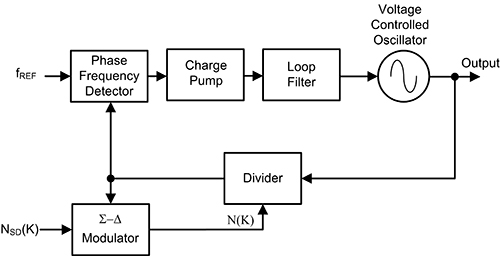

Sintetizadores de malha de captura de fase N fracionário

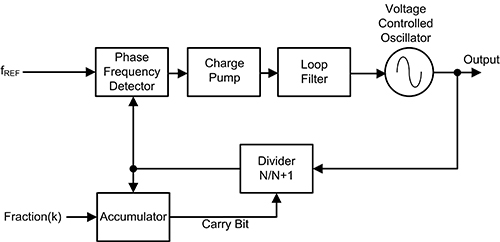

A resolução da frequência da PLL pode ser melhorada reduzindo o tamanho do passo para serem menores que valores inteiros, ou seja, fazendo passos fracionários no divisor de malha (N). Isso é realizado variando dinamicamente ou "dithering" o valor de contagem regressiva. Isto significa que o ajuste do divisor mantém o valor N para um número fixo de ciclos da frequência de saída da PLL e é periodicamente escalonado para um valor diferente, como N + 1. Por exemplo, se o ajuste do divisor for 4 para três períodos de referência e 5 para o quarto ciclo de referência, a contagem regressiva efetiva é 4,25. Uma maneira de fazer isso é usar um acumulador, como mostrado na Figura 3.

Figura 3: O diagrama de blocos de um sintetizador PLL N fracionário usando um acumulador para modular a contagem do divisor. (Fonte da imagem: DigiKey)

Figura 3: O diagrama de blocos de um sintetizador PLL N fracionário usando um acumulador para modular a contagem do divisor. (Fonte da imagem: DigiKey)

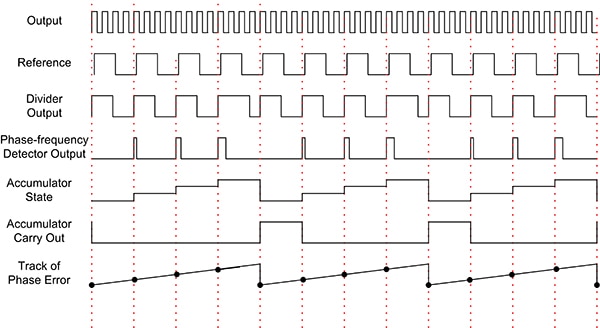

O acumulador conta os pulsos de saída do divisor e, a cada M, sendo M o módulo do acumulador, emite um bit de transporte que altera a entrada do divisor. A Figura 4 continua o exemplo de ajuste de um divisor fracionário de 4,25.

Figura 4: diagrama de temporização de um sintetizador N fracionário usando um acumulador. (Fonte da imagem: DigiKey)

Figura 4: diagrama de temporização de um sintetizador N fracionário usando um acumulador. (Fonte da imagem: DigiKey)

O acumulador é acionado pela saída dividida e conta o módulo quatro, ou seja, M é igual a quatro. Cada quarto pulso gera uma saída de transporte, que aumenta a contagem de divisor em um. O acumulador é reiniciado e recomeça a contagem. O aumento no ajuste do divisor desloca a frequência de saída, o que resulta num erro de defasamento de fase acumulada. O rastreio do erro de fase mostra o valor do pulso em função do tempo.

O ajuste médio do divisor é 4,25, mas a saída do sintetizador é modulada por fase, resultando em tons espúrios na saída. Olhando para o estado do acumulador, é óbvio que ele rastreia o erro de fase. Isso pode ser usado para remover a modulação, como mostrado na Figura 5.

Figura 5: utilizando o estado do acumulador com conversor D/A para cancelar a modulação de fase devido ao dithering de N fracionário. (Fonte da imagem: DigiKey)

Figura 5: utilizando o estado do acumulador com conversor D/A para cancelar a modulação de fase devido ao dithering de N fracionário. (Fonte da imagem: DigiKey)

O estado do acumulador é convertido para analógico por um conversor digital-analógico (D/A), escalonado e subtraído da saída do detector de frequência e fase para cancelar a modulação de fase devido ao dithering de N fracionário. Isso tem de ser feito com muito cuidado; se o sinal de correção não coincidir exatamente com o erro de fase, então haverá tons espúrios na saída.

Introduza o modulador sigma-delta

A periodicidade no acumulador é a causa de saídas espúrias do sintetizador. Se o acumulador for substituído por um modulador sigma-delta, então técnicas digitais podem ser aplicadas para modular a contagem do divisor de forma a minimizar respostas e ruídos espúrios. Essa substituição é mostrada na Figura 6.

Figura 6: A substituição do acumulador por um modulador sigma-delta permite a aplicação de técnicas digitais para variar a contagem do divisor, a fim de reduzir as respostas espúrias. (Fonte da imagem: DigiKey)

Figura 6: A substituição do acumulador por um modulador sigma-delta permite a aplicação de técnicas digitais para variar a contagem do divisor, a fim de reduzir as respostas espúrias. (Fonte da imagem: DigiKey)

Existem realmente duas técnicas digitais comuns que são empregadas na topologia de modulação sigma-delta. A primeira envolve aumentar o número de contagens do divisor N em uma faixa mais ampla de valores, de modo que o fator de divisão médio produzirá o valor de divisão fracionário desejado. Isso reduzirá os espúrios fracionários primários. O sintetizador baseado no acumulador varia a contagem entre dois estados. Esse é um método de modulação de primeira ordem. Uma PLL fracionária sigma-delta de ordem n modula o contador N entre 2n valores diferentes. Por exemplo, um modulador de terceira ordem alternaria entre oito valores diferentes do divisor e um modulador de quarta ordem alternaria entre 16 valores diferentes do divisor.

A segunda técnica digital — também conhecida como dithering — envolve a aleatorização da sequência 2N para que seja pseudoaleatória. Embora ainda mantendo uma relação fracionária média do divisor, ela converte os espúrios fracionários em ruído aleatório formatado de uma maneira que possa ser filtrado pela PLL.

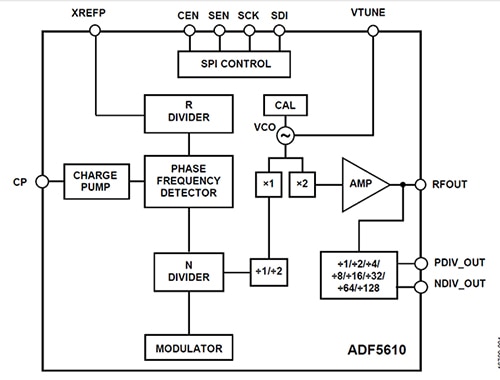

Uma versão comercial de um sintetizador N fracionário sigma-delta é o ADF5610BCCZ, da Analog Devices, um sintetizador N fracionário de baixo ruído de 0,57 megahertz (MHz) a 14,6 GHz com um VCO integrado (Figura 7).

Figura 7: um diagrama de blocos do ADF5610BCCZ da Analog Devices que suporta tanto as configurações de sintetizador de N fracionário quanto inteiro. (Fonte da imagem: Analog Devices)

Figura 7: um diagrama de blocos do ADF5610BCCZ da Analog Devices que suporta tanto as configurações de sintetizador de N fracionário quanto inteiro. (Fonte da imagem: Analog Devices)

O ADF5610 requer um oscilador de referência externo e um filtro de malha. Ele possui um VCO integrado com uma frequência fundamental de 3650 MHz a 7300 MHz. Essas frequências são dobradas internamente e direcionadas para o pino RFOUT. Existe uma saída diferencial que permite dividir a frequência do VCO duplicada por fatores de 1, 2, 4, 8, 16, 32, 64 ou 128, capaz de gerar frequências RF de saída tão baixa quanto 57 MHz.

O ADF5610 utiliza um avançado modulador sigma-delta com um módulo fracionário de 24 bits que atinge níveis de espúrios excepcionalmente baixos. Como em todos os sintetizadores que usam um modulador sigma-delta, esse dispositivo usa técnicas de processamento de sinal digital para encontrar a relação média desejada do divisor fracionário. Esse processo, com clock fixado na taxa PFD, produz um ruído de modulação de saída chamado ruído de quantização com uma resposta de frequência passa-alta. O filtro de malha externo passa-baixa é utilizado para filtrar esse ruído de quantização para um nível abaixo do ruído de fase do VCO, evitando assim que o ruído contribua para o ruído de fase geral do sistema.

O ADF5610 também inclui um modo de frequência exato para erro de frequência de 0 hertz (Hz). Esse modo é capaz de gerar frequências exatas entre os passos de limite N inteiros adjacentes enquanto ainda utiliza o módulo completo do acumulador de fase de 24 bits. Ele atinge passos de frequência exatos com uma elevada taxa de comparação do detector de fase, permitindo que a PLL mantenha um desempenho excelente contra ruído de fase e espúrios nesse modo.

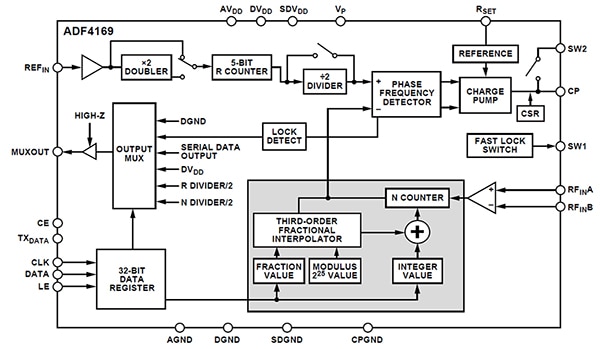

O ADF4169CCPZ-RL7 da Analog Devices é outro sintetizador PLL que pode ser configurado tanto como dispositivo N inteiro quanto N fracionário. Funciona com uma largura de banda RF de até 13,5 GHz com modulação e geração de forma de onda. Utiliza uma entrada de frequência de referência, VCO e filtro de malha externos. Tem um modulador sigma-delta de terceira ordem para síntese N fracionária que pode ser desativado, permitindo que o dispositivo seja executado no modo N inteiro (Figura 8).

Figura 8: O ADF4169CCPZ-RL7 da Analog Devices usa um modulador sigma-delta de terceira ordem. (Fonte da imagem: Analog Devices)

Figura 8: O ADF4169CCPZ-RL7 da Analog Devices usa um modulador sigma-delta de terceira ordem. (Fonte da imagem: Analog Devices)

O sintetizador ADF4158WCCPZ-RL7 destina-se a ser utilizado em radares de onda contínua de frequência modulada (FMCW). É capaz de lidar com vários tipos de formas de ondas moduladas no domínio de frequência, incluindo dente de serra e rampas triangulares. Essa é uma funcionalidade especial necessária em aplicações de radar.

Conclusão

O aumento das taxas de dados em barramentos de comunicações seriais de alta velocidade exige que os projetistas olhem para além dos sintetizadores digitais diretos — que funcionam melhor abaixo dos 3 GHz — para soluções de clock de sistema. Os sintetizadores de frequência baseados em PLL que usam topologias N inteiras e fracionárias fornecem sinais estáveis e de baixo ruído para clock de alta frequência, comunicações de dados seriais e aplicações de radar para frequências de até dezenas de gigahertz.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.