Por Que e Como Usar as FPGAs da Efinix para IA/ML de Imagens — Parte 1: Primeiros Passos

Contributed By DigiKey's European Editors

2023-04-20

Nota do editor: Novas abordagens às arquiteturas FPGA trazem um controle mais refinado e maior flexibilidade para atender às necessidades de aprendizagem de máquinas (ML) e inteligência artificial (IA). A Parte 1 desta série de duas partes apresenta uma dessas arquiteturas da Efinix e como começar a utilizá-la usando uma placa de desenvolvimento. A Parte 2 discute a interface da placa de desenvolvimento com dispositivos externos e periféricos, tais como uma câmera.

As FPGAs desempenham um papel crítico em muitas aplicações, desde o controle e segurança industrial até robótica, aeroespacial e automotiva. Graças à natureza flexível do núcleo lógico programável e seus amplos recursos de interface, um caso de uso crescente para FPGAs está no processamento de imagens quando a inferência ML está para ser implantada. As FPGAs são ideais para implementar soluções que possuem várias interfaces de câmeras de alta velocidade. Além disso, as FPGAs também permitem a implementação de pipelines de processamento dedicado na lógica, removendo assim os gargalos que estariam associados a soluções baseadas em CPU ou GPU.

Para muitos desenvolvedores, entretanto, suas aplicações requerem mais funcionalidade ML/IA e controle ou roteamento e lógica mais refinados, muito além do que as arquiteturas FPGA clássicas com blocos lógicos combinatórios (CLBs) podem fornecer. Novas abordagens para as arquiteturas FPGA resolvem essas questões. Por exemplo, a arquitetura Quantum da Efinix utiliza um bloco de Lógica e Roteamento Intercambiáveis (XLR).

Este artigo discute as principais características e atributos da arquitetura FPGA da Efinix, enfatizando seus recursos de IA/ML e apresentando implementações para o mundo real. Em seguida, aborda uma placa de desenvolvimento e ferramentas associadas que os desenvolvedores podem usar para iniciar rapidamente seu próximo projeto de IA/ML de imagem.

Dispositivos FPGA Efinix

A Efinix oferece atualmente duas linhas de dispositivos. Inicialmente, apresentou a família Trion, que oferece densidades lógicas de 4000 (4K) a 120K elementos lógicos (LEs) e é fabricada usando um processo SMIC 40LL. A mais nova linha de dispositivos, a família Titanium, oferece densidades lógicas de 35K a 1 milhão (1M) de elementos lógicos e é fabricada no muito popular nó TSMC 16 nanômetros (nm).

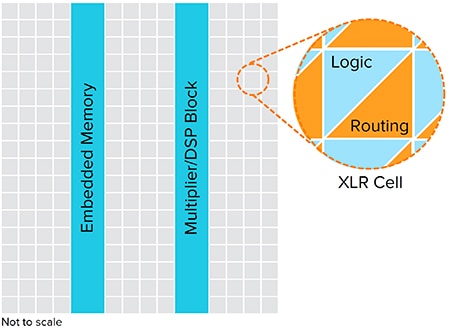

Ambas as ofertas são baseadas em torno da arquitetura Quantum, que é única no mundo FPGA. A arquitetura padrão FPGA é baseada em CLBs que, no nível mais simples, contêm uma tabela de pesquisa (LUT) e flip flops. As CLBs implementam equações lógicas que são então interligadas via roteamento. A arquitetura Quantum da Efinix se afasta da lógica distinta e dos blocos de roteamento com o bloco XLR.

O que torna um bloco XLR único é que ele pode ser configurado para funcionar como uma célula lógica com uma LUT, um registrador e um somador ou uma matriz de roteamento. Essa abordagem oferece uma arquitetura mais refinada que oferece flexibilidade de roteamento, permitindo implementações que são pesadas em termos lógicos ou em termos de roteamento para atingir o desempenho desejado.

Figura 1: o que torna um bloco XLR único é que ele pode ser configurado para funcionar tanto como uma célula lógica com uma LUT, um registrador e um somador, quanto como uma matriz de roteamento. (Fonte da imagem: Efinix)

Figura 1: o que torna um bloco XLR único é que ele pode ser configurado para funcionar tanto como uma célula lógica com uma LUT, um registrador e um somador, quanto como uma matriz de roteamento. (Fonte da imagem: Efinix)

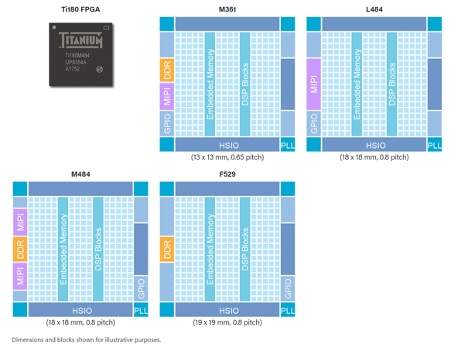

Sendo a família mais nova, os dispositivos Titanium oferecem as características mais avançadas para o desenvolvedor (Figura 2). Junto com o núcleo XLR, eles fornecem links seriais multi-gigabit que operam a 16 gigabits por segundo (Gbps) ou a 25,8 Gbps, dependendo do dispositivo selecionado. Esses links multi-gigabit são cruciais para permitir a transferência de dados de alta velocidade dentro e fora do chip.

Figura 2: a FPGA Ti180 Titanium vem em uma variedade de opções, dependendo dos requisitos de largura do barramento, E/S e memória. (Fonte da imagem: Efinix)

Figura 2: a FPGA Ti180 Titanium vem em uma variedade de opções, dependendo dos requisitos de largura do barramento, E/S e memória. (Fonte da imagem: Efinix)

Os dispositivos Titanium também fornecem uma ampla variedade de recursos de interface de entrada/saída (E/S) que podem ser agrupadas como E/S de uso geral (GPIO) e que podem suportar padrões de E/S simples, tais como CMOS de baixa tensão (LVCMOS) a 3,3 volts, 2,5 volts e 1,8 volts.

Para interface de alta velocidade e diferencial, os dispositivos Titanium fornecem E/S de alta velocidade (HSIO) que suportam padrões de E/S simples, como LVCMOS a 1,2 volts, 1,5 volts, SSTL e HSTL. Os padrões diferenciais de E/S suportados pela HSIO incluem sinalização diferencial de baixa tensão (LVDS), SSTL diferencial e HSTL.

As FPGAs modernas também exigem memória de alta largura de banda estreitamente acoplada, que é usada para armazenar quadros de imagem para aplicações de processamento de imagem, dados de amostra para processamento de sinal e, naturalmente, para executar sistemas operacionais e software para processadores implementados dentro da FPGA. A variedade de dispositivos Titanium oferece a capacidade de interface com DDR4 (dynamic data rate four) e DDR4(x) de baixa potência (LPDDR4(x)). Dependendo do dispositivo Titanium selecionado, o suporte da largura do barramento é x32 (J) ou x16 (M), enquanto alguns dispositivos não têm suporte LPDDR4 (L).

As FPGAs Titanium são baseadas em SRAM e requerem uma memória de configuração, sendo a configuração do dispositivo realizada tanto por mestre/escravo SPI (Serial Peripheral Interconnect) ou JTAG. Para garantir que esse método de configuração seja seguro, a FPGA Titanium usa criptografia AES GCM do bitstream, juntamente com AES GCM e RSA-4096 para fornecer autenticação do bitstream. Uma segurança forte como essa é necessária, uma vez que as FPGAs são implantadas na borda onde agentes maliciosos poderiam acessar e manipular seu comportamento.

Apresentação da placa de desenvolvimento

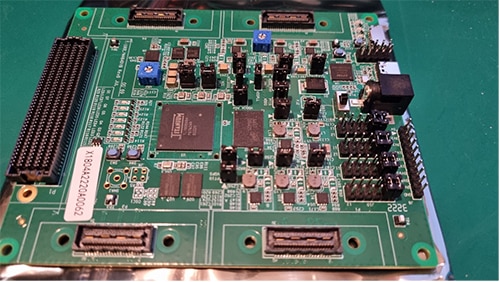

As placas de desenvolvimento formam um elemento crítico do processo de avaliação da FPGA, uma vez que podem ser usadas para explorar os recursos de um dispositivo e aplicações de protótipos, ajudando assim a reduzir o risco geral. A primeira placa de desenvolvimento disponível para avaliar as FPGAs Titanium e iniciar a prototipagem de aplicações é a Ti180 M484 (Figura 3). A placa possui um conector FPGA Mezzanine Card (FMC) e quatro conectores Samtec QSE.

Figura 3: junto com uma FPGA Titanium, o kit de desenvolvimento Ti180 M484 apresenta um conector FMC e quatro conectores Samtec QSE. (Fonte da imagem: Adam Taylor)

Figura 3: junto com uma FPGA Titanium, o kit de desenvolvimento Ti180 M484 apresenta um conector FMC e quatro conectores Samtec QSE. (Fonte da imagem: Adam Taylor)

A FPGA Ti180 instalada nessa placa de desenvolvimento fornece 172K células XLR, 32 clocks globais, 640 elementos processadores digitais de sinais (DSP) e 13 megabits (Mbits) de RAM embarcados. Os elementos DSP fornecem a capacidade de implementar multiplicações de ponto fixo 18 x 19 e multiplicações de 48 bits. Esse DSP também pode ser otimizado para operações SIMD (única instrução, múltiplos dados) rodando em uma configuração dupla ou quádrupla. Os elementos DSP também podem ser configurados para realizar operações de ponto flutuante.

Como a maioria das placas de desenvolvimento, a placa de desenvolvimento Ti180 fornece LEDs e botões simples. Seu verdadeiro poder, no entanto, vem em seus recursos de interface. A placa de desenvolvimento Ti180 fornece um conector FMC de poucos pinos que permite a conexão de uma ampla variedade de periféricos. Por ser um padrão amplamente utilizado, existem muitos cartões FMC que permitem a interface com conversores analógico/digital de alta velocidade (ADC), conversores digital/analógico (DAC), redes e soluções de memória/armazenamento.

Além da conexão FMC, a placa fornece quatro conectores Samtec QSE que permitem que o desenvolvedor acrescente placas de expansão. Esses conectores QSE são usados para fornecer entradas e saídas MIPI, com cada conector QSE fornecendo uma entrada ou saída MIPI.

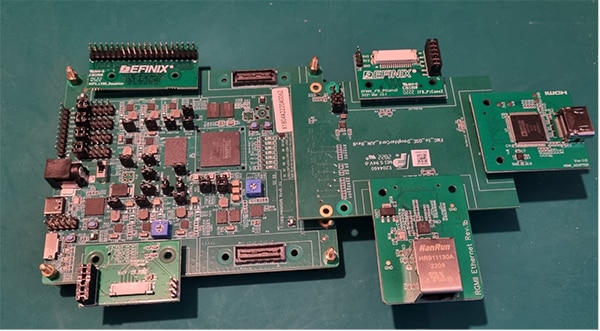

Figura 4: o kit de desenvolvimento Ti180 M484 é mostrado com sua versátil variedade de opções de expansão baseada em conectores QSE e FMC. (Fonte da imagem: Adam Taylor)

Figura 4: o kit de desenvolvimento Ti180 M484 é mostrado com sua versátil variedade de opções de expansão baseada em conectores QSE e FMC. (Fonte da imagem: Adam Taylor)

A placa Ti180 também fornece 256 Mbits de LPDDR4 para suportar a memória de alto desempenho necessária em aplicações de processamento de imagem ou sinal. Além disso, a placa de desenvolvimento oferece uma variedade de opções de clock em 25, 33,33, 50 e 74,25 megahertz (MHz), que pode ser usada com o loop de bloqueio de fase do dispositivo (PLL) para gerar diferentes frequências internas.

A capacidade de reprogramar e depurar em tempo real na placa durante o desenvolvimento é crítica e requer uma conexão JTAG, que é fornecida na placa por uma interface USB-C. Também é fornecida memória não-volátil na forma de dois dispositivos flash NOR de 256 Mbit que podem ser usados para demonstrar a solução de configuração.

A placa é alimentada por um adaptador de energia universal de 12 volts que está incluído na caixa. Também está incluído um break out FMC-para-QSE, juntamente com placas de expansão baseadas em QSE para HDMI, Ethernet, MIPI e LVDS. Para demonstrar a capacidade de processamento de imagem da Ti180, também são fornecidas uma placa filha RPI duplo e duas placas de câmera IMX477.

O ambiente de software

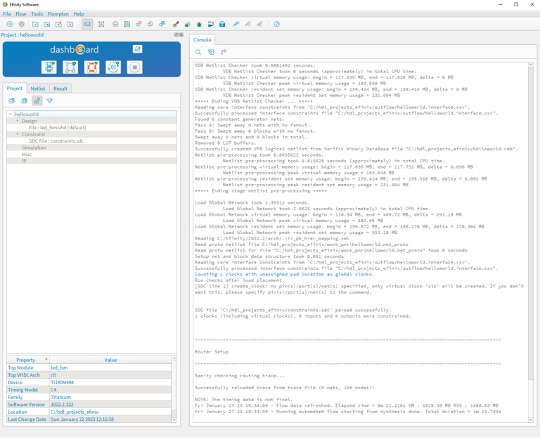

A implementação de projetos visando a placa de desenvolvimento Ti180 utiliza o software Efinity da Efinix. O software permite a geração de um fluxo de bits via síntese e local e rota. Ele também fornece aos desenvolvedores blocos de propriedade intelectual (IP), análise de temporização e depuração em chip.

Note que é necessária uma placa de desenvolvimento para ter acesso ao software Efinity. Ao contrário de outros fornecedores, porém, a ferramenta não possui versões diferentes que requerem licenciamento adicional.

Dentro do Efinity, novos projetos são criados visando o dispositivo selecionado. Os arquivos RTL podem então ser adicionados ao projeto e as restrições criadas para a sincronização e o projeto das E/S. É dentro do Efinity que os desenvolvedores também são capazes de implementar o projeto de E/S, utilizando a HSIO, GPIO e E/S especializadas.

Figura 5: dentro do Efinity, novos projetos são criados visando o dispositivo selecionado. (Fonte da imagem: Adam Taylor)

Figura 5: dentro do Efinity, novos projetos são criados visando o dispositivo selecionado. (Fonte da imagem: Adam Taylor)

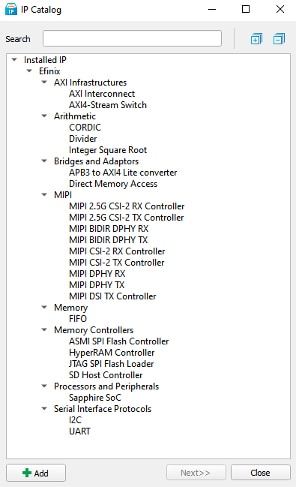

Um elemento crítico do projeto da FPGA é o aproveitamento do IP, especialmente para IPs complexos como interconexões AXI, controladores de memória e processadores softcore. O Efinity fornece aos desenvolvedores uma variedade de blocos IP que podem ser usados para acelerar o processo de projeto.

Figura 6: o Efinity fornece aos desenvolvedores um catálogo de IPs que eles podem utilizar para acelerar o processo de projeto. (Fonte da imagem: Adam Taylor)

Figura 6: o Efinity fornece aos desenvolvedores um catálogo de IPs que eles podem utilizar para acelerar o processo de projeto. (Fonte da imagem: Adam Taylor)

Enquanto as FPGAs são excelentes na implementação de estruturas de processamento paralelo, muitos projetos de FPGA incluem processadores softcore. Esses proporcionam a capacidade de implementar processamento sequencial, tais como comunicações em rede. Para permitir a implantação dos processadores softcore nos dispositivos Efinix, o Efinity fornece a ferramenta de configuração SoC (sistema sobre chip) Sapphire. A Sapphire permite que o desenvolvedor defina um sistema multiprocessador que possui tanto caches quanto cache coerente entre vários processadores, juntamente com a capacidade de executar um sistema operacional Linux embarcado. Dentro da Sapphire, o desenvolvedor pode escolher entre um e quatro processadores softcore.

O processador softcore que está sendo implementado é a CPU soft VexRiscV, que é baseada na arquitetura do conjunto de instruções RISC-V. O processador VexRiscV é uma implementação de 32 bits que possui extensões para uso de pipeline e oferece um conjunto de recursos configuráveis, tornando-o ideal para implementação em dispositivos Efinix. As configurações opcionais incluem um multiplicador, instruções atômicas, extensões de ponto flutuante e instruções comprimidas. Dependendo da configuração do sistema SoC, o desempenho irá variar entre 0,86 e 1,05 DMIPS/MHz.

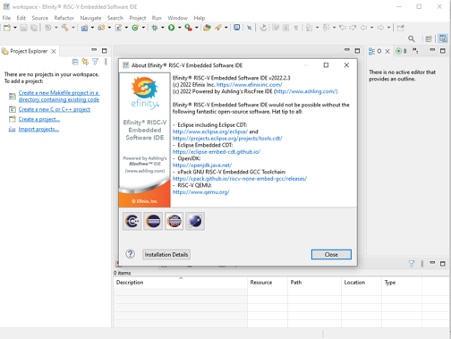

Uma vez projetado e implementado o ambiente de hardware no dispositivo Efinix, o software aplicativo pode ser desenvolvido utilizando a IDE Ashling RiscFree. Ashling RiscFree é uma IDE baseada em Eclipse que permite a criação e compilação de software aplicativo, juntamente com a depuração no alvo para o ajuste fino do aplicativo antes da implantação.

Figura 7: a Ashling RiscFree é uma IDE baseada em Eclipse que permite a criação e compilação de software aplicativo, juntamente com a depuração no alvo. (Fonte da imagem: Adam Taylor)

Figura 7: a Ashling RiscFree é uma IDE baseada em Eclipse que permite a criação e compilação de software aplicativo, juntamente com a depuração no alvo. (Fonte da imagem: Adam Taylor)

Se uma solução Linux embarcada estiver sendo desenvolvida, todos os artefatos de inicialização necessários são fornecidos, incluindo o First Stage Boot Loader, OpenSBI, U-Boot e Linux usando Buildroot. De modo alternativo, o desenvolvedor pode usar o FreeRTOS se uma solução em tempo real for necessária.

Implementação de IA

A implementação de IA da Efinix é baseada na operação softcore do RISC-V. Isso aproveita a capacidade de instrução personalizada do processador RISC-V para permitir a aceleração das soluções TensorFlow Lite. O uso do processador RISC-V também permite aos usuários criar instruções personalizadas que podem ser usadas como parte do pré-processamento ou pós-processamento seguindo a inferência da IA, criando uma solução mais responsiva e determinística.

Para começar a implementar uma IA, o primeiro passo é explorar o model zoo Efinix, que é uma biblioteca de modelos de IA/ML otimizados para sua tecnologia avançada. Para os desenvolvedores que trabalham com os dispositivos Efinix, o model zoo pode ser acessado e a rede pode ser treinada usando os Notebooks Jupyter ou o Google Colab. Uma vez que a rede tenha sido treinada, ela pode ser convertida de um modelo de ponto flutuante para um modelo quantizado usando o conversor TensorFlow Lite.

Uma vez no formato TensorFlow Lite, o acelerador tinyML da Efinix pode ser usado para criar uma solução implementável na solução RISC-V. O gerador tinyML permite ao desenvolvedor personalizar a implementação do acelerador e gerar os arquivos do projeto. Quando implantada dessa forma, a aceleração pode variar entre 4x e 200x, dependendo da arquitetura selecionada e da personalização.

Conclusão

Os dispositivos Efinix oferecem aos desenvolvedores flexibilidade graças à sua arquitetura XLR única. A cadeia de ferramentas fornece a capacidade de não apenas implementar o projeto RTL, mas também implementar soluções SoC complexas que implantam processadores RISC-V softcore. A construção baseada no SoC softcore é uma solução IA/ML que permite a implantação da inferência ML.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.