Por que e como usar FPGAs Efinix para geração de imagens AI/ML Parte 2: Captura e processamento de imagens

Contributed By DigiKey's European Editors

2023-05-05

Nota do editor: Novas abordagens às arquiteturas FPGA trazem um controle mais refinado e maior flexibilidade para atender às necessidades de aprendizagem de máquinas (ML) e inteligência artificial (IA). A Parte 1 desta série de duas partes apresenta uma dessas arquiteturas da Efinix e como começar a usá-la em uma placa de desenvolvimento. Aqui, a Parte 2 discute a interface da placa de desenvolvimento com dispositivos externos e periféricos, como uma câmera, e como aproveitar o FPGA para remover gargalos no processamento de imagens.

Os FPGAs desempenham um papel crítico em muitas aplicações, desde o controle e segurança industrial até robótica, aeroespacial e automotiva. Graças à natureza flexível do núcleo lógico programável e aos seus amplos recursos de interface, um caso de uso crescente para FPGAs é o processamento de imagens, no qual o aprendizado de máquina (ML) pode ser implementado. Os FPGAs são ideais para implementar soluções com várias interfaces de câmera de alta velocidade, graças à sua estrutura lógica paralela. Além disso, os FPGAs também permitem o uso de um pipeline de processamento dedicado na lógica, removendo assim os gargalos de recursos compartilhados que estariam associados a soluções baseadas em CPU ou GPU.

Esta segunda olhada nos FPGAs Titanium da Efinix examinará a aplicação de processamento de imagens de referência que acompanha a placa de desenvolvimento Ti180 M484 do FPGA. O objetivo é entender as partes constituintes do projeto e identificar onde a tecnologia FPGA permite a remoção de gargalos ou possibilita outros benefícios para os desenvolvedores.

O projeto de referência baseado no Ti180 M484

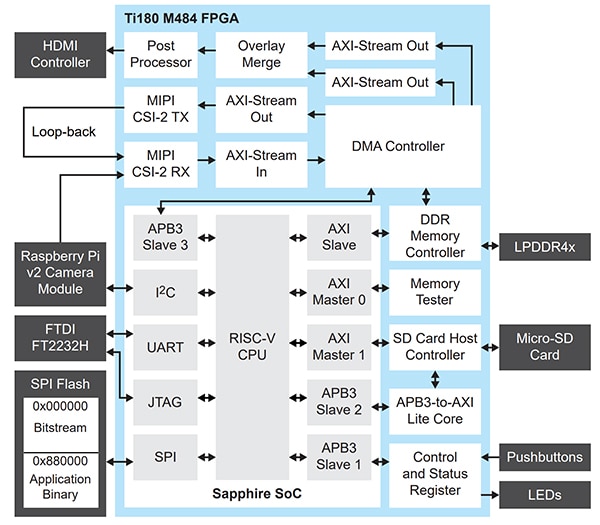

Conceitualmente, o projeto de referência (Figura 1) recebe imagens de várias câmeras MIPI (Mobile Industry Processor Interface), executa o buffer de quadros no LPDDR4x e, em seguida, gera as imagens em um display HDMI (Interface multimídia de alta definição). Uma placa de mezanino FPGA (FMC) e quatro interfaces Samtec QSE na placa são usadas para fornecer as entradas da câmera e a saída HDMI.

Figura 1: Conceitualmente, o projeto de referência Ti180 M484 recebe imagens de várias câmeras MIPI, executa o buffer de quadros no LPDDR4x e, em seguida, gera as imagens em um display HDMI. >(Fonte da imagem: Efinix)

Figura 1: Conceitualmente, o projeto de referência Ti180 M484 recebe imagens de várias câmeras MIPI, executa o buffer de quadros no LPDDR4x e, em seguida, gera as imagens em um display HDMI. >(Fonte da imagem: Efinix)

A placa de expansão FMC para QSE é usada em conjunto com a placa filha HDMI para fornecer o caminho do vídeo de saída, enquanto três conectores QSE são usados para fazer a interface com as câmeras MIPI DFRobot SEN0494. Se não houver várias câmeras MIPI disponíveis, uma única câmera poderá ser usada fazendo um ciclo de volta no canal de uma única câmera para simular câmeras adicionais.

Em um nível mais amplo, esta aplicação pode parecer simples. No entanto, receber vários fluxos MIPI de alta definição (HD) em uma alta taxa de quadros é um desafio. É nesse ponto que a tecnologia FPGA é vantajosa, pois permite que os projetistas utilizem vários fluxos MIPI em paralelo.

A arquitetura do projeto de referência aproveita as estruturas de processamento paralelo e sequencial com o FPGA. As estruturas paralelas são usadas para implementar o pipeline de processamento de imagens, enquanto um processador RISC-V fornece o processamento sequencial usado para as tabelas de pesquisa (LUTs) do FPGA.

O pipeline de processamento de imagens pode ser dividido em dois elementos em muitos sistemas de processamento de imagens baseados em FPGA, ou seja, os fluxos de entrada e saída. O fluxo de entrada é conectado à interface da câmera/sensor, e as funções de processamento são aplicadas à saída do sensor. Essas funções podem incluir conversão Bayer, balanço de branco automático e outros aprimoramentos. No fluxo de saída, a imagem é preparada para exibição. Isso inclui a alteração dos espaços de cores (por exemplo, RGB para YUV) e o pós-processamento para o formato de saída desejado, como HDMI.

Em geral, a cadeia de processamento da imagem de entrada opera na taxa de clock do pixel do sensor. Isso tem uma temporização diferente da cadeia de saída, que é processada na frequência de exibição de saída.

Um buffer de quadro é usado para conectar a entrada ao pipeline de processamento de saída, que geralmente é armazenado em uma memória externa de alto desempenho, como LPDDR4x. Esse buffer de quadros é desacoplado entre os pipelines de entrada e saída, permitindo o acesso ao buffer de quadros por meio de acesso direto à memória na frequência de clock apropriada.

O projeto de referência do Ti180 usa uma abordagem semelhante aos conceitos descritos acima. O pipeline de processamento das imagens de entrada implementa um núcleo de propriedade intelectual (IP) do receptor MIPI de interface serial da câmera 2 (CSI-2), que é desenvolvido com base na entrada/saída (E/S) compatível com a camada física MIPI (MIPI D-PHY) do FPGA Titanium. MIPI é uma interface desafiadora, pois usa sinalização diferencial e de terminação simples no mesmo par diferencial, além de comunicações de baixa e alta velocidade. A integração do MIPI D-PHY na E/S do FPGA reduz a complexidade do projeto da placa de circuito e, ao mesmo tempo, reduz a lista de materiais (BOM).

Com o fluxo de imagem da câmera recebido, o projeto de referência converte a saída do MIPI CSI-2 RX em um fluxo AXI (Advanced eXtensible Interface). Um fluxo AXI é uma interface unidirecional de alta velocidade que fornece um fluxo de dados de um mestre para um escravo. Os sinais de handshaking para transferência entre um mestre e um escravo são fornecidos (tvalid e tready) junto com sinais de banda lateral. Esses sinais de banda lateral podem ser usados para transmitir informações da temporização da imagem, como o início do quadro e o fim da linha.

O fluxo AXI é ideal para aplicações de processamento de imagens e permite que a Efinix forneça uma variedade de IPs de processamento de imagens que podem ser facilmente integrados à cadeia de processamento, conforme exigido pela aplicação.

Após serem recebidos, os dados de imagem MIPI CSI-2 e os sinais de temporização são convertidos em um fluxo AXI e inseridos em um módulo de acesso direto à memória (DMA), que escreve o quadro de imagem no LPDDR4x e atua como buffer de quadros.

Esse módulo de DMA opera sob o controle do núcleo RISC-V no FPGA dentro de um sistema sobre chip (SoC) Sapphire. Esse SoC fornece controle, como parar e iniciar escritas do DMA, além de fornecer ao canal de escrita do DMA as informações necessárias para escrever corretamente os dados da imagem no LPDDR4x. Isso inclui informações sobre o local da memória e a largura e a altura da imagem definidas em bytes.

O canal de saída no projeto de referência lê as informações de imagem do buffer de quadros no LPDDR4x sob o controle do SoC RISC-V. Os dados são gerados pelo IP do DMA como um fluxo AXI, que é então convertido do formato RAW fornecido pelo sensor para o formato RGB (Figura 2) e preparado para saída pelo transmissor HDMI ADV7511 da Analog Devices na placa.

Figura 2: Exemplo de imagens geradas pelo projeto de referência. (Fonte da imagem: Adam Taylor)

Figura 2: Exemplo de imagens geradas pelo projeto de referência. (Fonte da imagem: Adam Taylor)

O uso do DMA também permite que o RISC-V SoC Sapphire acesse as imagens armazenadas no buffer de quadros, as estatísticas abstratas e as informações da imagem. O SoC Sapphire também é capaz de escrever sobreposições no LPDDR4x para que possam ser mescladas com o fluxo de vídeo de saída.

Os sensores de imagem CMOS (CISs) modernos têm vários modos de operação e podem ser configurados para fornecer processamento no chip, além de vários formatos de saída e esquemas de clock diferentes. Normalmente, essa configuração é fornecida por meio de uma interface I²C. No projeto de referência da Efinix, essa comunicação I²C com as câmeras MIPI é fornecida pelo processador RISC-V SoC Sapphire.

A integração do processador RISC-V no FPGA Titanium reduz o tamanho geral da solução final, pois elimina a necessidade de implementar máquinas de estado complexas no FPGA, que aumentam o risco do projeto, bem como processadores externos que aumentam a lista de materiais.

A inclusão do processador também permite o suporte com IP adicional para comunicação com o cartão MicroSD. Isso permite aplicações práticas em que pode ser necessário armazenar imagens para análise posterior.

Em geral, a arquitetura do projeto de referência Ti180 é otimizada para permitir uma solução compacta, de baixo custo e de alto desempenho, que permite aos desenvolvedores reduzir o custo da lista de materiais por meio da integração do sistema.

Um dos principais benefícios dos projetos de referência é que eles podem ser usados para dar o pontapé inicial no desenvolvimento de aplicações em hardware personalizado, permitindo que os desenvolvedores utilizem elementos essenciais do projeto e o desenvolvam com as personalizações necessárias. Isso inclui a capacidade de usar o fluxo TinyML da Efinix para implementar aplicações TinyML baseadas em visão executadas no FPGA. Isso pode aproveitar tanto a natureza paralela da lógica do FPGA quanto a capacidade de adicionar facilmente instruções personalizadas aos processadores RISC-V, permitindo a criação de aceleradores dentro da lógica do FPGA.

Implementação

Conforme discutido na Parte 1, a arquitetura Efinix é única, pois usa células XLR (eXchangeable Logic and Routing) para fornecer funcionalidade de roteamento e lógica. Um sistema de vídeo, como o projeto de referência, é um sistema misto, com muita lógica e roteamento: é necessária uma lógica extensa para implementar os recursos de processamento de imagem e um roteamento extenso para conectar as células IP nas frequências exigidas.

O projeto de referência usa aproximadamente 42% das células XLR dentro do dispositivo, deixando amplo espaço para acréscimos, incluindo aplicações personalizadas, como ML na borda.

O uso da RAM de bloco e dos blocos de processamento de sinal digital (DSP) também é muito eficiente, usando apenas 4 dos 640 blocos de DSP e 40% dos blocos de memória (Figura 3).

|

Figura 3: A alocação de recursos na arquitetura Efinix mostra que apenas 42% das células XLR são usadas, deixando amplo espaço para processos adicionais. (Fonte da imagem: Adam Taylor)

Na E/S do dispositivo, a interface DDR para o LPDDR4x é usada para fornecer a memória da aplicação para o SoC Sapphire e os buffers de quadros da imagem. Todos os recursos MIPI dedicados ao dispositivo são utilizados juntamente com 50% das malhas de captura de fase (Figura 4).

|

Figura 4: Registro da interface e dos recursos de E/S usados. (Fonte da imagem: Adam Taylor)

A E/S de uso geral (GPIO) é usada para fornecer comunicações I²C juntamente com várias interfaces conectadas ao SoC Sapphire, incluindo NOR FLASH, USB UART e cartão SD. O HSIO é usado para fornecer a saída de vídeo de alta velocidade para o transmissor HDMI do ADC7511.

Um dos elementos cruciais ao projetar com FPGAs não é apenas a implementação e o ajuste do projeto no FPGA, mas também a capacidade de posicionar o projeto lógico no FPGA e obter o desempenho de temporização necessário quando roteado.

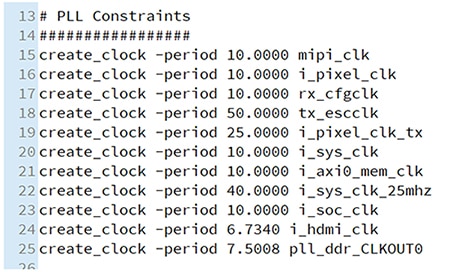

Já se foram os dias dos projetos de FPGA com domínio de clock único. Há vários clocks diferentes, todos executados em altas frequências no projeto de referência do Ti180. A tabela de temporização final mostra as frequências máximas alcançadas para os clocks no sistema. É nesse ponto que o desempenho de temporização solicitado também pode ser visto nas restrições (Figura 5), que têm uma frequência de clock máxima de 148,5 megahertz (MHz) para o clock de saída HDMI.

Figura 5: Restrições de clock para o projeto de referência. (Fonte da imagem: Adam Taylor)

Figura 5: Restrições de clock para o projeto de referência. (Fonte da imagem: Adam Taylor)

A implementação da temporização em relação às restrições mostra o potencial da estrutura XLR do FPGA Titanium, pois reduz o possível atraso de roteamento, aumentando assim o desempenho do projeto (Figura 6).

|

Figura 6: A implementação da temporização em relação às restrições mostra o potencial da estrutura XLR do FPGA Titanium para reduzir o possível atraso de roteamento, aumentando assim o desempenho do projeto. (Fonte da imagem: Adam Taylor)

Conclusão

O projeto de referência Ti180 M484 demonstra claramente os recursos dos FPGAs da Efinix e do Ti180 em particular. O design aproveita várias das estruturas de E/S exclusivas para implementar um caminho de processamento de imagem complexo que suporta vários fluxos MIPI de entrada. Esse sistema de processamento de imagens opera sob o controle de um SoC Sapphire de núcleo leve, que implementa os elementos de processamento sequencial necessários da aplicação.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.