A arquitetura do co-processador: uma arquitetura de sistema embarcado para prototipagem rápida

2021-07-06

Nota do editor — Embora bem conhecida por seu desempenho e rendimento de processamento digital, a arquitetura de co-processador oferece ao projetista de sistemas embarcados oportunidades para implementar estratégias de gerenciamento de projetos, que melhoram tanto os custos de desenvolvimento quanto o tempo de colocação no mercado. Este artigo, focado especificamente na combinação de um microcontrolador discreto (MCU) e uma matriz de portas programáveis no campo (FPGA) discreto, mostra como esta arquitetura se presta a um processo de projeto eficiente e iterativo. Alavancando fontes pesquisadas, descobertas empíricas e estudos de caso, os benefícios desta arquitetura são explorados e aplicações exemplares são fornecidas. Após a conclusão deste artigo, o projetista de sistemas embarcados terá uma melhor compreensão de quando e como implementar esta versátil arquitetura de hardware.

Introdução

O projetista de sistemas embarcados se encontra em uma conjuntura de restrições de projeto, expectativas de desempenho e preocupações com cronograma e orçamento. De fato, até mesmo as contradições nas modernas palavras e frases de gerenciamento de projetos ressaltam ainda mais a natureza precária deste papel: "falhar rapidamente"; "ser ágil"; "ser à prova de futuro"; e "ser disruptivo!". A acrobacia envolvida até mesmo na tentativa de satisfazer essas expectativas pode ser assustadora e, no entanto, elas têm sido faladas e continuam a ser reforçadas em todo o mercado. O que é necessário é uma abordagem de projeto, que permite a implementação de um processo iterativo evolutivo e, assim como a maioria dos sistemas embarcados, ele começa com a arquitetura de hardware.

A arquitetura de co-processador, uma arquitetura de hardware conhecida por combinar os pontos fortes tanto da unidade microcontroladora (MCU) quanto das tecnologias de matriz de porta programável no campo (FPGA), pode oferecer ao projetista de embarcados um processo capaz de atender até mesmo os requisitos mais exigentes, e ainda permite a flexibilidade necessária para enfrentar tanto os desafios conhecidos como os desconhecidos. Ao fornecer hardware capaz de se adaptar iterativamente, o projetista pode demonstrar progresso, atingir marcos críticos e tirar o máximo proveito do rápido processo de prototipagem.

Dentro deste processo estão os marcos-chave do projeto, cada um com seu próprio valor único para agregar ao esforço de desenvolvimento. Ao longo deste artigo, estes serão referidos pelos termos a seguir: O marco do Processamento Digital de Sinais com o Microcontrolador, o marco do Gerenciamento do Sistema com o Microcontrolador e o marco da Implantação do Produto.

Pela conclusão deste artigo, será demonstrado que uma arquitetura de hardware flexível pode ser mais adequada ao projeto de sistemas embarcados modernos do que uma abordagem mais rígida. Além disso, esta abordagem pode resultar em melhorias tanto no custo do projeto quanto no tempo de colocação no mercado. Argumentos, com exemplos, e estudos de caso serão utilizados para defender esta posição. Observando o valor de cada marco dentro da flexibilidade de projeto que esta arquitetura proporciona, torna-se claro que uma arquitetura de hardware adaptável é uma poderosa comandante para impulsionar o projeto de sistemas embarcados.

Explorando os pontos fortes da arquitetura do co-processador: flexibilidade de projeto e processamento de alto desempenho

Uma aplicação comum para projetos FPGA é a interface direta com um conversor analógico-digital de alta velocidade (ADC). O sinal é digitalizado, lido na FPGA, e então alguns algoritmos de processador digital de sinais (DSP) são aplicados a este sinal. Por último, a FPGA toma decisões com base nos resultados.

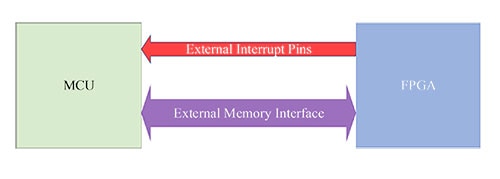

Tal aplicação servirá de exemplo ao longo deste artigo. Além disso, a Figura 1 ilustra uma arquitetura genérica de co-processador, onde o MCU e FPGA são conectados através da interface de memória externa do MCU. A FPGA é tratada como se fosse uma peça de memória externa estática de acesso aleatório (SRAM). Os sinais voltam da FPGA para a MCU e servem como linhas de interrupção de hardware e indicadores de status. Isto permite que a FPGA indique estados críticos para a MCU, tais como comunicar que uma conversão ADC está pronta, ou que ocorreu uma falha, ou que outro evento digno de nota aconteceu.

Figura 1: Diagrama genérico do co-processador (MCU + FPGA). (Fonte da imagem: CEPD)

Figura 1: Diagrama genérico do co-processador (MCU + FPGA). (Fonte da imagem: CEPD)

Os pontos fortes da abordagem do co-processador são provavelmente melhor vistos dentro dos resultados de cada um dos marcos acima mencionados. O valor é avaliado não apenas listando as realizações de uma tarefa ou fase, mas também avaliando a capacitação que essas realizações permitem. As respostas às seguintes perguntas ajudam a avaliar o valor geral dos resultados de um marco miliário:

- O progresso de outros membros da equipe pode agora continuar mais rapidamente, à medida que as dependências e os gargalos do projeto são removidos?

- Como as realizações do marco miliário possibilitam mais caminhos de execução paralelos?

O processamento do sinal digital com o marco do microcontrolador

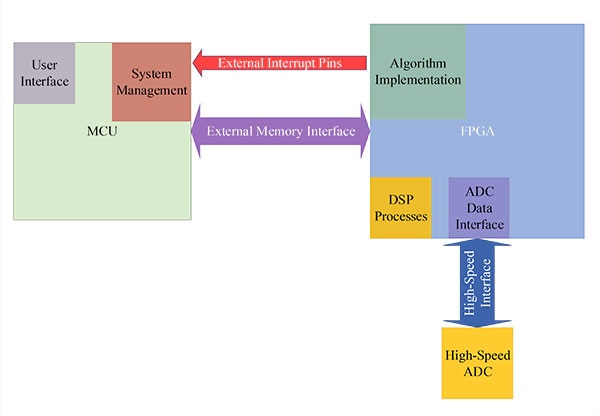

Figura 2: Arquitetura - processamento de sinal digital com o microcontrolador. (Fonte da imagem: CEPD)

Figura 2: Arquitetura - processamento de sinal digital com o microcontrolador. (Fonte da imagem: CEPD)

A primeira etapa de desenvolvimento que esta arquitetura de hardware permite coloca o MCU na frente e no centro. Sendo todas as coisas iguais, o desenvolvimento do MCU e do software executável consome menos recurso e tempo que o desenvolvimento do FPGA e da linguagem descritiva de hardware (HDL). Assim, ao iniciar o desenvolvimento do produto com o MCU como processador primário, os algoritmos podem ser implementados, testados e validados mais rapidamente. Isto permite que bugs algorítmicos e lógicos sejam descobertos no início do processo de projeto, e isto também permite que partes substanciais da cadeia de sinais sejam testadas e validadas.

O papel da FPGA neste marco inicial é servir como uma interface de coleta de dados de alta velocidade. Sua tarefa é canalizar de forma confiável os dados do ADC de alta velocidade, alertar o MCU de que os dados estão disponíveis e apresentar esses dados na interface da memória externa do MCU. Embora esta função não inclua a implementação de processos DSP baseados em HDL ou outros algoritmos, ela é, no entanto, altamente crítica.

O desenvolvimento da FPGA realizado nesta fase estabelece a base para o sucesso final do produto, tanto dentro dos esforços de desenvolvimento do produto como na sua liberação para o mercado. Ao focar apenas na interface de baixo nível, o tempo adequado pode ser dedicado a testar estas operações essenciais. Somente quando a FPGA estiver desempenhando de forma confiável esta função de interface, este marco poderá ser concluído com confiança.

Os principais resultados deste marco inicial incluem os seguintes benefícios:

- O caminho completo do sinal - todas as amplificações, atenuações e conversões - terá sido testado e validado.

- O tempo e esforço de desenvolvimento do projeto terão sido reduzidos pela implementação inicial dos algoritmos no software (C/C++); isto é de considerável valor para a gerência e outras partes interessadas, que devem ver a viabilidade deste projeto antes de aprovar futuras fases de projeto.

- As lições aprendidas com a implementação dos algoritmos em C/C++ serão diretamente transferíveis para implementações HDL - através do uso de ferramentas de software para HDL, por exemplo, Xilinx HLS.

O gerenciamento do sistema com o marco do microcontrolador

Figura 3: Arquitetura - gerenciamento do sistema com o microcontrolador. (Fonte da imagem: CEPD)

Figura 3: Arquitetura - gerenciamento do sistema com o microcontrolador. (Fonte da imagem: CEPD)

A segunda etapa de desenvolvimento, que esta abordagem de co-processador oferece, é definida pela mudança dos processos e implementações de algoritmos do DSP a partir do MCU à FPGA. A FPGA ainda é responsável pela interface de alta velocidade do ADC, porém, ao assumir essas outras funções, a velocidade e o paralelismo oferecidos pela FPGA são plenamente utilizados. Além disso, ao contrário do MCU, múltiplas instâncias dos processos DSP e canais de algoritmo podem ser implementadas e executadas simultaneamente.

Com base na lição aprendida com a implementação do MCU, o projetista leva esta confiança adiante para este próximo marco. Ferramentas, como o já mencionado Vivado HLS da Xilinx, fornecem uma tradução funcional do código C/C++ executável para HDL sintetizável. Agora, as restrições de tempo, parâmetros de processo e outras preferências do usuário ainda devem ser definidas e implementadas, entretanto, a funcionalidade central é perseverada e traduzida para o tecido da FPGA.

Para este marco, o papel do MCU é o de um gerente de sistemas. Os registradores de status e controle dentro da FPGA são monitorados, atualizados e reportados pelo MCU. Além disso, o MCU gerencia a interface do usuário (UI). Esta UI pode assumir a forma de servidor web acessado através de uma conexão ethernet ou Wi-Fi, ou pode ser uma interface industrial sensível ao toque que dá acesso aos usuários no ponto de uso. A principal lição do novo e mais refinado papel do MCU é esta: ao serem liberados das tarefas de processamento computacional intensivo, tanto o MCU quanto a FPGA estão agora sendo alavancados em tarefas para as quais eles são bem adequados.

Os principais resultados deste marco histórico incluem estes benefícios:

- A execução rápida e paralela dos processos e implementações de algoritmos do DSP estão sendo fornecidos pela FPGA.O MCU fornece uma UI responsiva e simplificada e gerencia os processos do produto.

- Tendo sido desenvolvido e validado pela primeira vez dentro do MCU, os riscos algorítmicos foram mitigados e estas mitigações são traduzidas em HDL sintetizável. Ferramentas, como Vivado HLS, fazem desta tradução um processo mais fácil. Além disso, os riscos específicos da FPGA podem ser mitigados através de ferramentas de simulação integradas, tais como o pacote de design Vivado.

- As partes interessadas não são expostas a riscos significativos ao transferir os processos para a FPGA. Pelo contrário, elas conseguem ver e desfrutar dos benefícios que a velocidade e o paralelismo da FPGA proporcionam. As melhorias de desempenho mensuráveis são observadas e o foco agora pode ser dado à preparação deste projeto para a fabricação.

O marco da implantação do produto

Com o processamento computacionalmente intensivo sendo abordado dentro da FPGA, e o MCU lidando com suas funções de gerenciamento de sistema e interface do usuário, o produto está pronto para a implantação. Agora, este documento não advoga para contornar as versões Alfa e Beta; entretanto, a ênfase para este marco são as capacidades que a arquitetura de co-processador fornece à implantação do produto.

Tanto o MCU quanto a FPGA são dispositivos atualizáveis em campo. Vários avanços têm sido feitos para tornar as atualizações FPGA tão acessíveis quanto as atualizações de software. Além disso, como a FPGA está dentro do espaço de memória endereçável do MCU, o MCU pode servir como o ponto de acesso para todo o sistema: recebendo tanto atualizações para si mesmo quanto para a FPGA. As atualizações podem ser programadas condicionalmente, distribuídas e personalizadas por usuário final. Por último, os registros de usuários e casos de uso podem ser mantidos e associados a implementações de construções específicas. A partir desses conjuntos de dados, o desempenho pode continuar a ser refinado e aprimorado mesmo depois que o produto estiver no campo.

Talvez os pontos fortes desta capacidade de atualização total do sistema não sejam mais ressaltados do que em aplicações baseadas no espaço. Uma vez lançado um produto, a manutenção e as atualizações devem ser realizadas remotamente. Isto poderia ser tão simples quanto mudar as condições lógicas, ou tão complicado quanto atualizar um esquema de modulação das comunicações. A programabilidade oferecida pelas tecnologias FPGA e a arquitetura do co-processador podem acomodar toda esta gama de capacidades, tudo isso enquanto oferece opções de componentes resistentes à radiação.

A lição principal e final deste marco é a redução progressiva dos custos. Reduções de custos, alterações na lista de materiais (BOM) e outras otimizações também podem ocorrer neste marco. Durante as implantações no campo, pode ser descoberto que o produto pode operar igualmente bem com um MCU menos caro, ou com uma FPGA menos capaz. Devido ao co-processador, os projetistas de arquitetura não ficam presos usando componentes cujas capacidades excedem as necessidades de sua aplicação. Além disso, caso um componente não esteja disponível, a arquitetura permite que novos componentes sejam integrados ao projeto. Este não é o caso de uma arquitetura de chip único, sistema em um chip (SoC), ou com um DSP ou MCU de alto desempenho, que tenta lidar com todo o processamento do produto. A arquitetura do co-processador é uma boa mistura de capacidade e flexibilidade dando ao projetista mais opções e liberdades tanto nas fases de desenvolvimento quanto na liberação para o mercado.

Apoio à pesquisa e estudos de casos relacionados

Exemplo de comunicações via satélite

Em resumo, o valor de um co-processador é descarregar a unidade de processamento primário para que as tarefas sejam executadas sobre hardware, no qual acelerações e racionalização podem ser aproveitadas. A vantagem de tal escolha de projeto é um aumento líquido da velocidade computacional e das capacidades e, como este artigo argumenta, uma redução no custo e no tempo de desenvolvimento. Talvez um dos domínios mais convincentes para estes benefícios seja na área dos sistemas de comunicação espacial.

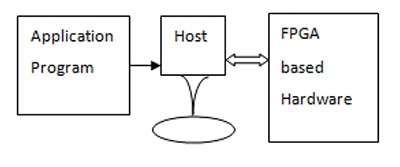

Em sua publicação, FPGA based hardware as coprocessor, G. Prasad e N. Vasantha detalham como o processamento de dados dentro de uma FPGA combina as necessidades computacionais dos sistemas de comunicação via satélite sem os altos custos de engenharia não-recorrente (NRE) de circuitos integrados de aplicação específica (ASICs) ou as limitações específicas de aplicação de um processador de arquitetura rígida. Assim como foi descrito no Processamento do sinal digital com o marco do microcontrolador, seu projeto começa com o processador de aplicação executando a maioria dos algoritmos computacionalmente intensivos. A partir deste ponto de partida, eles identificam as seções-chave do software que consomem a maioria dos ciclos de clock da unidade central de processamento (CPU) e migram estas seções para a implementação do HDL. A representação gráfica é altamente similar ao que foi apresentado até agora, no entanto, eles optaram por representar o Programa de Aplicação como seu próprio bloco independente, como pode ser percebido no Host (Processador) ou no Hardware baseado na FPGA.

Figura 4: Programa de aplicação, processador host e hardware baseado em FPGA - exemplo de utilização em comunicações via satélite.

Figura 4: Programa de aplicação, processador host e hardware baseado em FPGA - exemplo de utilização em comunicações via satélite.

Ao utilizar uma interface de interconexão de componentes periféricos (PCI) e o acesso direto à memória do processador host (DMA), o desempenho do periférico é drasticamente aumentado. Isto é observado principalmente dentro das melhorias para o processo de Derandomização. Quando este processo foi realizado no software do processador host, houve claramente um gargalo na resposta em tempo real do sistema. No entanto, quando transferida para a FPGA, os seguintes benefícios foram observados:

- O processo de Derandomização executou em tempo real sem causar gargalos

- A sobrecarga computacional do processador host foi significativamente reduzida, e agora ele poderia desempenhar melhor uma função desejada de registros.

- O desempenho total do sistema inteiro foi ampliado.

Tudo isso foi conseguido sem os custos associados a um ASIC, e enquanto desfrutava da flexibilidade da lógica programável [5]. As comunicações via satélite apresentam desafios consideráveis, e esta abordagem pode comprovadamente atender a estes requisitos, e continuar a proporcionar flexibilidade de projeto.

Exemplo de infoentretenimento automotivo

Os sistemas de entretenimento dentro dos automóveis são características distintivas para consumidores exigentes. Ao contrário da maioria da eletrônica automotiva, estes dispositivos são altamente visíveis e espera-se que proporcionem tempo de resposta e desempenho excepcionais. No entanto, os projetistas muitas vezes estão espremidos entre as necessidades atuais do projeto e a flexibilidade, que as características futuras exigirão. Para este exemplo, as necessidades de implementação de processamento de sinais e comunicações sem fio serão usadas para destacar os pontos fortes da arquitetura de hardware do co-processador.

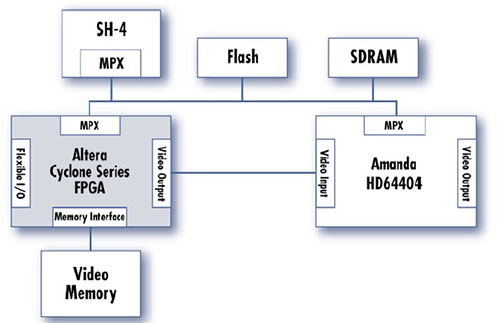

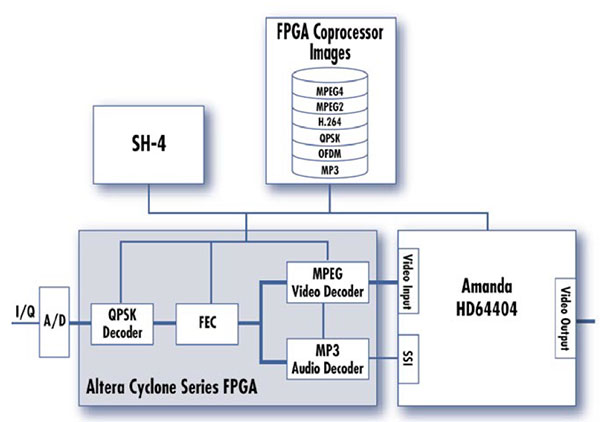

Uma das arquiteturas predominantes de sistemas de entretenimento automotivo utilizadas foi publicada pela Delphi Delco Electronics Systems Corporation. Esta arquitetura empregou um MCU SH-4 com um ASIC complementar, o periférico HD64404 Amanda da Hitachi. Esta arquitetura satisfez mais de 75% da funcionalidade básica de entretenimento do mercado automotivo; no entanto, faltava-lhe a capacidade de lidar com aplicações de processamento de vídeo e comunicações sem fio. Ao incluir uma FPGA dentro desta arquitetura existente, mais flexibilidade e capacidade podem ser adicionadas a esta abordagem de projeto já existente.

Figura 5: arquitetura do co-processador de infoentretenimento FPGA, exemplo 1.

Figura 5: arquitetura do co-processador de infoentretenimento FPGA, exemplo 1.

A arquitetura da Figura 5 é adequada tanto para o processamento de vídeo quanto para o gerenciamento de comunicações sem fio. Ao empurrar as funcionalidades do DSP para a FPGA, o processador Amanda pode servir uma função de gerenciamento do sistema e é liberado para implementar uma pilha de comunicações sem fio. Como tanto a Amanda quanto a FPGA têm acesso à memória externa, os dados podem ser rapidamente trocados entre os processadores e componentes do sistema.

Figura 6: arquitetura do co-processador de infoentretenimento FPGA, exemplo 2.

Figura 6: arquitetura do co-processador de infoentretenimento FPGA, exemplo 2.

O segundo infoentretenimento da Figura 6 destaca a capacidade da FPGA de tratar tanto os dados analógicos de alta velocidade recebidos quanto o manuseio da compressão e codificação necessárias para aplicações de vídeo. Na verdade, toda esta funcionalidade pode ser empurrada para a FPGA e, através do uso de processamento paralelo, todas elas podem ser tratadas em tempo real.

Ao incluir uma FPGA dentro de uma arquitetura de hardware existente, o desempenho comprovado do hardware existente pode ser aliado à flexibilidade e a prova de futuro. Mesmo dentro dos sistemas existentes, a arquitetura do co-processador oferece opções aos projetistas, que de outra forma não estariam disponíveis [6].

Vantagens da prototipagem rápida

Em sua essência, o processo de prototipagem rápida se esforça para cobrir uma quantidade substancial da área de desenvolvimento de produtos, executando tarefas em paralelo, identificando "bugs" e problemas de projeto rapidamente, e validando dados e caminhos de sinal, especialmente aqueles dentro do caminho crítico de um projeto. No entanto, para que este processo produza resultados realmente otimizados e eficientes, deve haver experiência suficiente nas áreas de projeto necessárias.

Tradicionalmente, isto significa que deve haver um engenheiro de hardware, um engenheiro de software embarcado ou de DSP, e um engenheiro de HDL. Agora, há muitos profissionais interdisciplinares, que podem ser capazes de satisfazer múltiplas funções; no entanto, ainda há uma sobrecarga substancial do projeto envolvido na coordenação desses esforços.

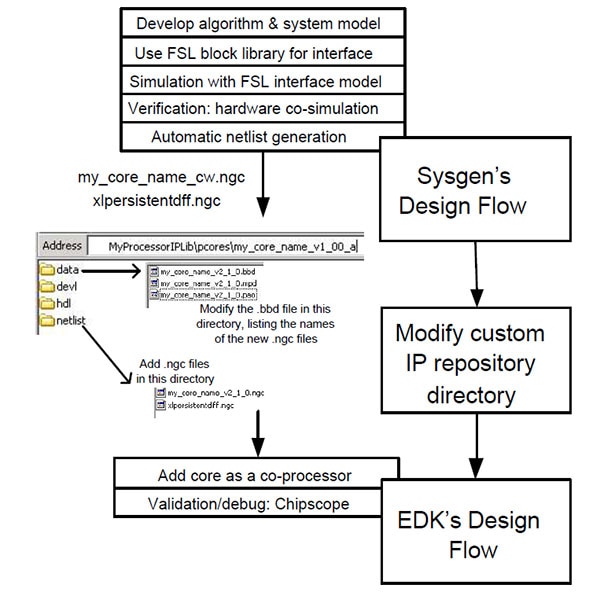

Em seu artigo, An FPGA based rapid prototyping platform for wavelet coprocessors, os autores promovem a idéia de que o uso de uma arquitetura de co-processador permite que um único engenheiro DSP cumpra todas essas funções, de forma eficiente e eficaz. Para este estudo, a equipe começou a projetar e simular a funcionalidade desejada do DSP dentro da ferramenta Simulink da MATLAB. Isto serviu a duas funções primárias, na medida em que 1) verificou o desempenho desejado através de simulação, e 2) serviu como uma linha de base para a qual as futuras escolhas de projeto poderiam ser comparadas e referenciadas.

Após a simulação, as funcionalidades críticas foram identificadas e divididas em diferentes núcleos – estes são componentes e processadores de núcleo flexível que podem ser sintetizados dentro de uma FPGA. O passo mais importante durante este trabalho foi definir a interface entre estes núcleos e componentes e comparar o desempenho da troca de dados com o desempenho desejado e simulado. Este processo de projeto está estreitamente alinhado com o fluxo de projeto do Xilinx para sistemas embarcados e está resumido na Figura 7 abaixo.

Figura 7: Fluxo de projeto de implementação.

Figura 7: Fluxo de projeto de implementação.

Ao dividir o sistema em núcleos sintetizáveis, o engenheiro do DSP pode se concentrar nos aspectos mais críticos da cadeia de processamento de sinais. Ela/ele não precisa ser especialista em hardware ou HDL para modificar, rotear ou implementar diferentes processadores ou componentes de núcleo flexível dentro da FPGA. Desde que o projetista esteja ciente da interface e dos formatos dos dados, eles têm controle total sobre os caminhos do sinal e podem refinar o desempenho do sistema.

Descobertas empíricas – o discreto estudo de caso da transformada de cosseno

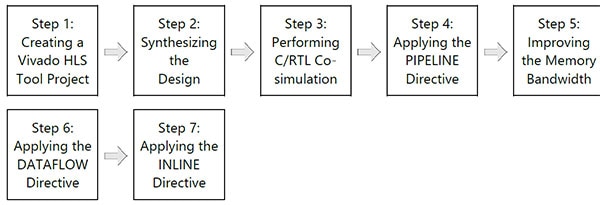

As descobertas empíricas não apenas confirmaram a flexibilidade aproveitada pela arquitetura de co-processador para o projetista de sistemas embarcados, mas também mostraram as opções de melhoria de desempenho disponíveis com as modernas ferramentas FPGA. Melhorias, como as mencionadas abaixo, podem não estar disponíveis ou podem ter menos impacto para outras arquiteturas de hardware. A transformada discreta de cosseno (DCT) foi selecionada como um algoritmo computacionalmente intensivo, e sua progressão de uma implementação baseada em C para uma implementação baseada em HDL estava no centro destas descobertas. O DCT foi escolhido porque este algoritmo é usado no processamento de sinais digitais para reconhecimento e filtragem de padrões [8]. As descobertas empíricas foram baseadas em um exercício de laboratório, que foi concluído pelo autor e colegas de trabalho, para obter a certificação Xilinx Alliance Partner durante 2020 - 2021.

As seguintes ferramentas e dispositivos foram utilizados neste esforço:

- Vivado HLS v2019

- O dispositivo para avaliação e simulação foi o xczu7ev-ffvc1156-2-e

Começando com a implementação baseada em C, o algoritmo DCT aceita duas matrizes de números de 16 bits; a matriz "a" é a matriz de entrada para o DCT, e a matriz "b" é a matriz de saída do DCT. A largura dos dados (DW) é portanto definida como 16, e o número de elementos dentro das matrizes (N) é 1024/DW, ou 64. Por último, o tamanho da matriz DCT (DCT_SIZE) é ajustado para 8, o que significa que é usada uma matriz de 8 x 8.

Seguindo a premissa deste artigo, a implementação do algoritmo baseado em C permite ao projetista desenvolver e validar rapidamente a funcionalidade do algoritmo. Embora seja uma consideração importante, esta validação coloca a funcionalidade em um peso maior do que o tempo de execução. Esta ponderação é permitida, já que a implementação final deste algoritmo será em uma FPGA, onde a aceleração do hardware, o desenrolamento do loop e outras técnicas estão prontamente disponíveis.

Figura 8: Fluxo de projeto Xilinx Vivado HLS.

Figura 8: Fluxo de projeto Xilinx Vivado HLS.

Uma vez criado o código DCT dentro da ferramenta Vivado HLS como um projeto, o próximo passo é começar a sintetizar o projeto para a implementação da FPGA. É neste próximo passo que alguns dos benefícios mais impactantes de mover a execução de um algoritmo de um MCU para uma FPGA se tornam mais aparentes – como referência, este passo é equivalente ao Gerenciamento do Sistema com o marco do Microcontrolador discutido acima.

As modernas ferramentas FPGA permitem um pacote de otimizações e aperfeiçoamentos que melhoram muito o desempenho de algoritmos complexos. Antes de analisar os resultados, há alguns termos importantes a ter em mente:

- Latência – O número de ciclos de clock necessários para executar todas as iterações do loop [10]

- Intervalo – O número de ciclos de clock antes que a próxima iteração de um loop começa a processar dados [11]

- BRAM – Memória de acesso aleatório em bloco

- DSP48E – Fatia de Processamento Digital de Sinais para a Arquitetura de Ultra-escala

- FF – Flipflop

- LUT – Tabela de pesquisa

- URAM – Memória Unificada de Acesso Aleatório (pode ser composta de um único transistor)

|

||||||||||||||||||||||||||||||||||||||||

Tabela 1: Resultados da otimização da execução do algoritmo FPGA (latência e intervalo).

|

Tabela 2: Resultados da otimização da execução do algoritmo FPGA (utilização de recursos).

Padrão

A configuração padrão de otimização vem do resultado inalterado da tradução do algoritmo baseado em C para HDL sintetizável. Nenhuma otimização está habilitada, e isto pode ser usado como referência de desempenho para entender melhor as outras otimizações.

Loop interno do pipeline

A diretiva PIPELINE instrui Vivado HLS a desenrolar os loops internos de modo que novos dados possam começar a ser processados enquanto os dados existentes ainda estão na pipeline. Assim, os novos dados não precisam esperar que os dados existentes estejam completos para que o processamento possa começar.

Loop externo da pipeline

Ao aplicar a diretiva PIPELINE ao loop externo, as operações do loop externo são agora conduzidas. Entretanto, as operações de loop interno agora ocorrem de forma concomitante. Tanto a latência quanto o tempo de intervalo são reduzidos pela metade através da aplicação direta ao loop externo.

Partição da matriz

Esta diretiva mapeia o conteúdo dos loops para as matrizes e, assim, nivela todo o acesso de memória aos elementos únicos dentro destas matrizes. Ao fazer isto, mais RAM é consumida, mas novamente, o tempo de execução deste algoritmo é reduzido pela metade.

Fluxo de dados

Esta diretiva permite ao projetista especificar o número destinado de ciclos de clock entre cada uma das leituras de entrada. Esta diretiva é suportada apenas para funções de alto nível. Somente loops e funções expostas a este nível serão beneficiadas por esta diretiva.

Em linha

A diretiva Em linha ou INLINE nivela todos os loops, tanto internos quanto externos. Ambos os processos de linha e coluna podem agora ser executados simultaneamente. O número de ciclos de clock necessários é mantido ao mínimo, mesmo que isso consuma mais recursos da FPGA.

Conclusão

A arquitetura de hardware do co-processador fornece ao projetista de embarcados uma plataforma de alto desempenho que mantém sua flexibilidade de projeto durante todo o desenvolvimento e lançamento anterior de produtos. Ao validar algoritmos primeiro em C ou C++, processos, dados e caminhos de sinal e funcionalidades críticas podem ser verificadas em um período de tempo relativamente curto. Então, ao traduzir os algoritmos intensivos do processador para o co-processador FPGA, o projetista pode desfrutar dos benefícios da aceleração do hardware e de um projeto mais modular.

Caso as peças se tornem obsoletas ou sejam necessárias otimizações, a mesma arquitetura pode permitir estas mudanças. Novos MCUs e novas FPGAs podem ser encaixadas no projeto, enquanto as interfaces podem permanecer relativamente intocadas. Além disso, como tanto o MCU quanto a FPGA são atualizáveis em campo, mudanças e otimizações específicas do usuário podem ser aplicadas no campo e remotamente.

Para finalizar, esta arquitetura combina a velocidade de desenvolvimento e a disponibilidade de um MCU com o desempenho e a capacidade de expansão de uma FPGA. Com otimizações e melhorias de desempenho disponíveis em cada etapa de desenvolvimento, a arquitetura do co-processador pode atender até mesmo as necessidades mais desafiadoras – tanto para os projetos de hoje como para os que vão além.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.