Por que e como aplicar transístores de efeito de campo de GaN em aplicações eficientes de alimentação chaveada de tensão mais alta

Contributed By DigiKey's North American Editors

2023-01-26

A eficiência energética é uma prioridade para os sistemas eletrônicos diante das exigências tanto da sociedade quanto regulatórias. Em particular, para aplicações que vão desde veículos elétricos (EVs) até comunicações de alta tensão e infra-estrutura industrial, a eficiência da conversão de energia e a densidade de potência são fundamentais para o sucesso do projeto.

Para atender a estes requisitos, os projetistas de sistemas de alimentação chaveada precisam deixar de usar transistores clássicos de efeito de campo de óxido-metal (MOSFETs) e transistores bipolares de porta isolada (IGBTs) baseados em silício (Si), pois estão se aproximando rapidamente de seus limites teóricos.

Em vez disso, os projetistas precisam considerar dispositivos baseados em materiais de ampla banda proibida (WBG) como o nitreto de gálio (GaN). Os dispositivos de GaN comutam mais rápido que os dispositivos de Si, lidam com níveis de tensão e potência mais altos, são muito menores para um determinado nível de potência e operam com uma eficiência muito maior.

Este artigo examinará os conceitos básicos do FETs de GaN, mostrará suas vantagens sobre os dispositivos de Si tradicionais em circuitos de alimentação chaveada, apresentará exemplos reais da Nexperia e discutirá sua aplicação.

Os princípios básicos dos FETs de GaN

Os elementos fundamentais nos circuitos de conversão de energia são as chaves semicondutoras de alta tensão. Os projetistas têm se concentrado em melhorar o desempenho desses dispositivos através da: diminuição das perdas de condução, reduzindo a resistência série do estado ligado, diminuição das perdas de chaveamento, aumentando as velocidades de transição e reduzindo os efeitos parasitas. Estes esforços de projeto têm sido, em geral, bem sucedidos para MOSFETs e IGBTs de silício, mas o ritmo de melhoria tem sido lento à medida que o funcionamento destes dispositivos atinge seus limites teóricos.

Como resultado, nos últimos anos foram introduzidos dispositivos WBG que utilizam carbeto de silício (SiC) e GaN, ao ponto de terem atingido o volume de produção. Estes dispositivos oferecem faixas de tensão de operação mais altas, tempos de chaveamento mais rápidos e maior eficiência.

A banda proibida de um semicondutor é a energia mínima necessária para excitar os elétrons para libertá-los do seu estado de ligação a um estado livre a fim de conduzir eletricidade (Tabela 1).

|

Tabela 1: Um resumo das principais propriedades que distinguem os semicondutores de ampla banda proibida — tais como GaN e SiC — do Si. (Fonte da tabela: Art Pini)

Os dispositivos fabricados com semicondutores de ampla banda proibida podem operar em tensões, frequências e temperaturas muito mais altas do que os materiais semicondutores convencionais como o Si. A banda proibida mais larga é particularmente importante para permitir que os dispositivos operem a temperaturas muito mais altas. A tolerância à alta temperatura significa que, em condições normais, estes dispositivos podem ser operados com níveis de potência muito mais altos. Os semicondutores WBG com um campo elétrico crítico mais elevado e maior mobilidade têm a menor resistência de saturação entre dreno-fonte (RDS(ON)), o que reduz as perdas por condução.

A maioria dos materiais de ampla banda proibida também tem altas velocidades dos elétrons livres, o que lhes permite trabalhar com velocidades de chaveamento mais altas.

Em comparação com o Si, que tem uma banda proibida de 1,12 elétron volts (eV), GaN e SiC são semicondutores compostos com bandas proibidas que são cerca de três vezes maiores a 3,4 eV e 3,3 eV, respectivamente. Isto significa que ambos podem suportar tensões e frequências mais altas.

A maior mobilidade dos elétrons do GaN o torna muito mais adequado para aplicações de alto desempenho e alta frequência. As velocidades de chaveamento mais rápidas e frequências de operação mais altas possibilitadas pelos FETs de potência de GaN resultam em um melhor controle de sinal, projetos de filtros passivos com frequências de corte mais altas e correntes de ondulação mais baixas. Isto permite o uso de indutores, capacitores e transformadores menores, resultando na redução do tamanho total e do peso.

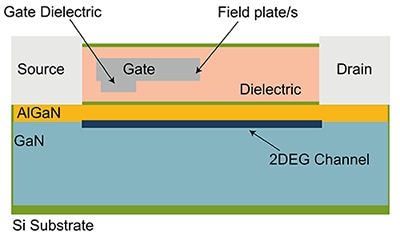

Os FETs de GaN são chamados de transistores de alta mobilidade de elétrons (HEMT). A alta mobilidade dos elétrons é uma função da estrutura do FET (Figura 1).

Figura 1: Uma vista de seção transversal de um FET de GaN baseado em um substrato de Si. (Fonte da imagem: Nexperia)

Figura 1: Uma vista de seção transversal de um FET de GaN baseado em um substrato de Si. (Fonte da imagem: Nexperia)

Os FETs de GaN utilizam as instalações existentes da produção dos CMOS de silício, tornando-os mais em conta. Uma camada de GaN é formada sobre o substrato de Si através da deposição uma camada de semente e uma camada graduada de GaN e nitreto de gálio e alumínio (AlGaN) como uma camada de isolação (não mostrada no diagrama) antes que a camada de GaN puro cresça. Uma segunda camada de AlGaN é depositada no topo da camada de GaN. Isto estabelece uma polarização piezoelétrica, com um excesso de elétrons sendo gerados imediatamente abaixo do AlGaN, que é um canal altamente condutivo. Este excesso de elétrons é conhecido como um gás de elétrons bidimensional (2DEG). O nome reflete a elevadíssima mobilidade dos elétrons nesta camada.

Uma região de depleção é formada sob a porta. A operação da porta é semelhante a um MOSFET de potência em silício em modo de enriquecimento, canal N. Uma tensão positiva aplicada à porta deste dispositivo o liga.

Esta estrutura é repetida várias vezes para formar um dispositivo de potência. O resultado final é uma solução fundamentalmente simples, elegante e econômica para o chaveamento de energia.

Para obter um dispositivo de maior tensão, a distância entre o Dreno e a Porta é aumentada. Como a resistividade do 2DEG GaN é muito baixa, o impacto na resistência aumentando a capacidade da tensão de bloqueio é muito menor quando comparado aos dispositivos de silício.

Os FETs de GaN podem ser construídos para operar em qualquer uma de duas configurações, modo de enriquecimento ou modo de depleção. Os FETs do modo de enriquecimento estão normalmente desligados, portanto uma tensão positiva em relação ao dreno/fonte deve ser aplicada à porta para ligar o FET. Os FETs do modo de depleção estão normalmente ligados, portanto, uma tensão de porta negativa em relação ao dreno/fonte deve ser aplicada para desligar o FET. Os FETs do modo de depleção são problemáticos em um sistema de alimentação porque uma polarização negativa tem que ser aplicada ao FET de GaN do modo de depleção antes de alimentar o sistema.

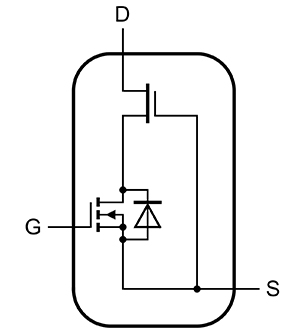

Uma maneira de contornar esta questão é combinar um FET de silício de baixa tensão com um FET de GaN do modo de depleção em uma configuração de circuito em cascata (Figura 2).

Figura 2: Um MOSFET de silício de baixa tensão em uma configuração de cascata com um FET de GaN em modo de depleção resulta na robustez da estrutura da porta de Si com as características melhoradas dos pulsos de alta tensão do dispositivo de GaN, assim como ter — no caso de um FET de GaN do modo de depleção — o dispositivo composto desligado na energização. (Fonte da imagem Nexperia)

Figura 2: Um MOSFET de silício de baixa tensão em uma configuração de cascata com um FET de GaN em modo de depleção resulta na robustez da estrutura da porta de Si com as características melhoradas dos pulsos de alta tensão do dispositivo de GaN, assim como ter — no caso de um FET de GaN do modo de depleção — o dispositivo composto desligado na energização. (Fonte da imagem Nexperia)

O circuito em cascata usa a estrutura da porta do MOSFET de Si que tem as vantagens de limites mais altos de acionamento da porta combinado com os CIs existentes acionadores de porta do MOSFET, e o FET de GaN do modo de depleção estando desligado na energização.

Uma das principais características dos FETs de GaN é sua alta eficiência. Isto se deve a: baixa resistência em série, que reduz as perdas de condução; seus tempos de chaveamento mais rápidos, que reduz as perdas de chaveamento; e sua menor carga de recuperação reversa, que é responsável por suas baixas perdas na recuperação reversa.

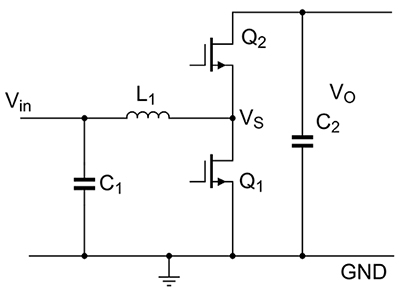

Usando uma topologia comum do conversor boost de meia ponte, é possível comparar a eficiência dos FETs de GaN e os MOSFETs de Si (Figura 3).

Figura 3: É mostrado o esquema de um conversor boost de meia ponte utilizado para comparar as eficiências dos MOSFETs e FETs de GaN através da troca dos transistores Q1 e Q2 com cada tipo. (Fonte da imagem: Nexperia)

Figura 3: É mostrado o esquema de um conversor boost de meia ponte utilizado para comparar as eficiências dos MOSFETs e FETs de GaN através da troca dos transistores Q1 e Q2 com cada tipo. (Fonte da imagem: Nexperia)

O conversor boost tem uma tensão de entrada de 240 volts, a saída é de 400 volts, e a frequência de chaveamento é de 100 quilohertz (kHz). As eficiências e perdas são comparadas em uma faixa de potência de até 3500 watts (Figura 4).

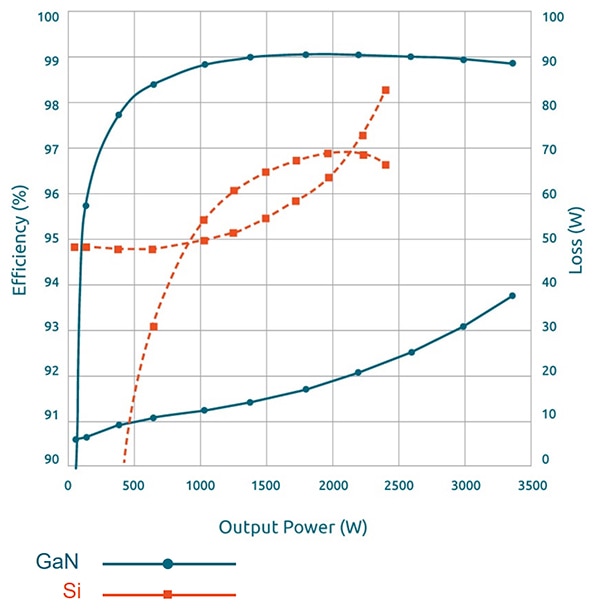

Figura 4: Uma comparação da eficiência e perda de potência entre FETs de GaN e MOSFETs em um circuito idêntico, mostrando as vantagens dos FETs de GaN. (Fonte da imagem Nexperia)

Figura 4: Uma comparação da eficiência e perda de potência entre FETs de GaN e MOSFETs em um circuito idêntico, mostrando as vantagens dos FETs de GaN. (Fonte da imagem Nexperia)

Os FETs de GaN têm uma eficiência cerca de 20% maior em comparação com os MOSFETs, e a perda de potência é menor por um fator de cerca de três. Com 2000 watts, a perda no MOSFETs é de cerca de 62 watts; nos FETs de GaN é de apenas 19 watts. Isto significa que o sistema de resfriamento pode ser menor, melhorando assim a eficiência volumétrica do conversor boost.

Menos óbvio é que a medição foi realizada até quase 3500 watts para o FET de GaN devido a seu limite máximo de tensão mais alta. Como tal, o FET de GaN tem uma vantagem definitiva.

Começando com GaN para tensões mais altas

Para aplicações de tensões mais altas, a Nexperia oferece dois FETs de GaN de 650 volts, o GAN063-650WSAQ e o GAN041-650WSBQ. Ambos são FETs de canal N que normalmente estão desligados. O GAN063-650WSAQ é dimensionado para lidar com uma tensão máxima de dreno-fonte de 650 volts e pode sustentar um transiente (com uma largura de pulso inferior a um microssegundo) de 800 volts. É dimensionado para uma corrente de dreno de 34,5 amperes (A) e uma dissipação de potência de 143 watts a 25°C. A resistência de dreno-fonte no estado ligado é tipicamente de 50 miliohms (mΩ), com um limite máximo de 60 mΩ.

O GAN041-650WSBQ tem a mesma tensão nominal máxima de dreno-fonte de 650 volts com o mesmo limite transitório de 800 volts. Ele difere pois pode lidar com uma corrente máxima de dreno de 47,2 A e uma dissipação máxima de potência de 187 watts à temperatura ambiente. Sua resistência típica do canal é de 35 mΩ, com um máximo de 41 mΩ.

Um projeto de referência da Nexperia usando o GAN063-650WSAQ em uma configuração de meia ponte é mostrado na Figura 5.

Figura 5: Um projeto recomendado para um estágio de energia de meia ponte usando FETs de GaN GAN063-650WSA. O esquema mostra apenas o acionador do FET e o estágio de saída de meia ponte, e componentes relacionados. (Fonte da imagem: Nexperia)

Figura 5: Um projeto recomendado para um estágio de energia de meia ponte usando FETs de GaN GAN063-650WSA. O esquema mostra apenas o acionador do FET e o estágio de saída de meia ponte, e componentes relacionados. (Fonte da imagem: Nexperia)

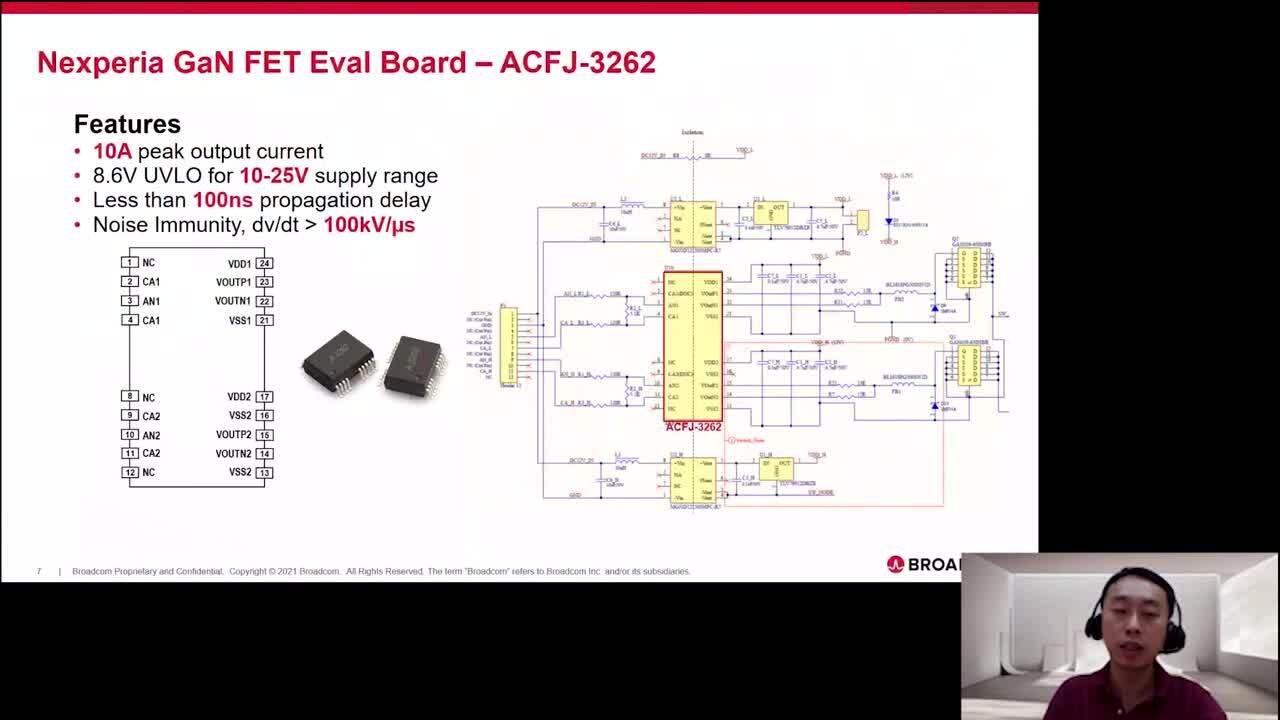

O esquema mostra o acionador de porta dupla isolada de alta/baixa Si8230, que é usado para acionar as portas dos FETs de GaN. A saída do acionador de porta é conectada à porta através de um resistor de porta de 30 Ω, que é necessário para todos os dispositivos de GaN. O resistor de porta controla o tempo de carga da capacitância de porta, afetando o desempenho dinâmico do chaveamento. As redes R-C entre o dreno e a fonte dos FETs também ajudam a controlar o desempenho do chaveamento. Os níveis do acionamento de porta para o FET de GaN estão entre 0 e 10 a 12 volts.

A alta velocidade de chaveamento dos FETs de GaN (normalmente na faixa de 10 a 11 nanossegundos (ns)) requer um layout cuidadoso para minimizar a indutância parasita, e o uso de snubbers RC para amortecer o zumbido devido a transientes de tensão e corrente. Há vários snubbers RC (R17 até 19 e C33 até 35) no projeto entre a fonte de alta tensão e o terra. Os snubbers reduzem o zumbido causado pela interação do FET de GaN e da rede de desvio. Os snubbers devem ser conectados o mais próximo possível do dreno do FET do lado de alta. Eles são implementados com resistores de montagem em superfície e capacitores de cerâmica de baixa resistência equivalente em série (ESR) para minimizar a indutância dos terminais.

A rede de componentes formada por R4, D1, C12 e C13 é uma fonte de alimentação bootstrap para o acionador de porta do lado de alta. D1 deve ser um diodo rápido e de baixa capacitância, pois sua capacitância de junção contribui para a perda de chaveamento. R4 limita a corrente de partida no carregamento; um valor na faixa de 10 a 15 Ω funciona bem.

Conclusão

Desde EVs a comunicações e infra-estrutura industrial, a necessidade de maior eficiência de conversão de energia e densidade de potência requer uma mudança das estruturas clássicas de Si. Como mostrado, os FETs de GaN proporcionam um caminho para projetos da próxima geração, oferecendo maiores tensões operacionais, tempos de chaveamento mais rápidos e maior eficiência. Componentes prontos para uso, apoiados em alguns casos por projetos de referência, ajudam os projetistas a colocar os projetos em funcionamento rapidamente.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.